|

CMSIS-Core (Cortex-M)

Version 5.1.1

CMSIS-Core support for Cortex-M processor-based devices

|

|

CMSIS-Core (Cortex-M)

Version 5.1.1

CMSIS-Core support for Cortex-M processor-based devices

|

Arm supplies CMSIS-Core device template files for the all supported Cortex-M processors and various compiler vendors. Refer to the list of Tested and Verified Toolchains for compliance.

These CMSIS-Core device template files include the following:

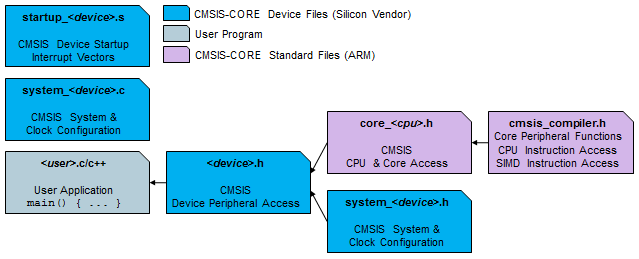

The detailed file structure of the CMSIS-Core device templates is shown in the following picture.

The CMSIS-Core processor files provided by Arm are in the directory .\CMSIS\Core\Include. These header files define all processor specific attributes do not need any modifications. The core_<cpu>.h defines the core peripherals and provides helper functions that access the core registers. One file is available for each supported Cortex-M processor:

| Header File | Processor |

|---|---|

| core_cm0.h | for the Cortex-M0 processor |

| core_cm0plus.h | for the Cortex-M0+ processor |

| core_cm3.h | for the Cortex-M3 processor |

| core_cm4.h | for the Cortex-M4 processor |

| core_cm7.h | for the Cortex-M7 processor |

| core_cm23.h | for the Cortex-M23 processor |

| core_cm33.h | for the Cortex-M33 processor |

| core_sc000.h | for the SecurCore SC000 processor |

| core_sc300.h | for the SecurCore SC300 processor |

| core_armv8mbl.h | for the Armv8-M Baseline processor |

| core_armv8mml.h | for the Armv8-M Mainline processor |

The CMSIS Software Pack defines several devices that are based on the various processors. The device related CMSIS-Core files are in the directory .\Device\ARM and include CMSIS-Core processor file explained before. The following sample devices are defined in the CMSIS-Pack description file ARM.CMSIS.pdsc:

| Family | Device | Description |

|---|---|---|

| ARM Cortex-M0 | ARMCM0 | Cortex-M0 based device |

| ARM Cortex-M0 plus | ARMCM0P | Cortex-M0+ based device |

| ARM Cortex-M3 | ARMCM3 | Cortex-M3 based device |

| ARM Cortex-M4 | ARMCM4 | Cortex-M4 based device without floating-point hardware |

| ARM Cortex-M4 | ARMCM4_FP | Cortex-M4 based device with floating-point hardware |

| ARM Cortex-M7 | ARMCM7 | Cortex-M4 based device without floating-point hardware |

| ARM Cortex-M7 | ARMCM7_FP | Cortex-M7 based device with single precision floating-point unit (FPU) |

| ARM Cortex-M7 | ARMCM7_DP | Cortex-M7 based device with double precision floating-point unit |

| ARM Cortex-M7 | ARMCM7 | Cortex-M7 based device without floating-point hardware |

| ARM Cortex-M23 | ARMCM23 | Cortex-M23 based device without TrustZone |

| ARM Cortex-M23 | ARMCM23_TZ | Cortex-M23 based device with TrustZone |

| ARM Cortex-M33 | ARMCM33 | Cortex-M33 based device without TrustZone, SIMD, FPU |

| ARM Cortex-M33 | ARMCM33_TZ | Cortex-M33 based device with TrustZone, no SIMD, no FPU |

| ARM Cortex-M33 | ARMCM33_DSP_FP | Cortex-M23 based device with SIMD, FPU, no TrustZone |

| ARM Cortex-M33 | ARMCM33_DSP_FP_TZ | Cortex-M23 based device with TrustZone, SIMD, FPU |

| ARM SC000 | ARM SC000 | SC000 based device |

| ARM SC300 | ARM SC300 | SC300 based device |

| ARMv8-M Baseline | ARMv8MBL | Armv8-M Baseline based device with TrustZone |

| ARMv8-M Mainline | ARMv8MML | Armv8-M Mainline based device with TrustZone |

| ARMv8-M Mainline | ARMv8MML_DP | Armv8-M Mainline based device with TrustZone and double precision FPU |

| ARMv8-M Mainline | ARMv8MML_SP | Armv8-M Mainline based device with TrustZone and single precision FPU |

| ARMv8-M Mainline | ARMv8MML_DSP | Armv8-M Mainline based device with TrustZone and SIMD |

| ARMv8-M Mainline | ARMv8MML_DSP_DP | Armv8-M Mainline based device with TrustZone, SIMD, and double precision FPU |

| ARMv8-M Mainline | ARMv8MML_DSP_SP | Armv8-M Mainline based device with TrustZone, SIMD, and single precision FPU |

To simplify the creation of CMSIS-Core device files, the following template files are provided that should be extended by the silicon vendor to reflect the actual device and device peripherals. Silicon vendors add to these template files the following information:

| Template File | Description |

|---|---|

| .\Device\_Template_Vendor\Vendor\Device\Source\ARM\startup_Device.s | Startup file template for Arm C/C++ Compiler. |

| .\Device\_Template_Vendor\Vendor\Device\Source\GCC\startup_Device.s | Startup file template for GNU GCC Arm Embedded Compiler. |

| .\Device\_Template_Vendor\Vendor\Device\Source\IAR\startup_Device.s | Startup file template for IAR C/C++ Compiler. |

| .\Device\_Template_Vendor\Vendor\Device\Source\system_Device.c | Generic system_Device.c file for system configuration (i.e. processor clock and memory bus system). |

| .\Device\_Template_Vendor\Vendor\Device\Include\Device.h | Generic device header file. Needs to be extended with the device-specific peripheral registers. Optionally functions that access the peripherals can be part of that file. |

| .\Device\_Template_Vendor\Vendor\Device\Include\system_Device.h | Generic system device configuration include file. |

Adapt Template Files to a Device

The following steps describe how to adopt the template files to a specific device or device family. Copy the complete all files in the template directory and replace:

Each template file contains comments that start with ToDo: that describe a required modification. The template files contain place holders:

| Placeholder | Replaced with |

|---|---|

| <Device> | the specific device name or device family name; i.e. LPC17xx. |

| <DeviceInterrupt> | a specific interrupt name of the device; i.e. TIM1 for Timer 1. |

| <DeviceAbbreviation> | short name or abbreviation of the device family; i.e. LPC. |

| Cortex-M# | the specific Cortex-M processor name; i.e. Cortex-M3. |

The device configuration of the template files is described in detail on the following pages: