|

CMSIS

Version 5.3.0

Cortex Microcontroller Software Interface Standard

|

|

CMSIS

Version 5.3.0

Cortex Microcontroller Software Interface Standard

|

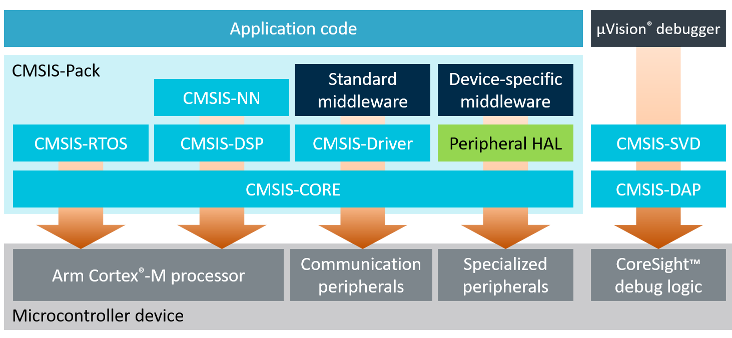

The Cortex Microcontroller Software Interface Standard (CMSIS) is a vendor-independent hardware abstraction layer for the Cortex®-M processor series and defines generic tool interfaces. The CMSIS enables consistent device support and simple software interfaces to the processor and the peripherals, simplifying software re-use, reducing the learning curve for microcontroller developers, and reducing the time to market for new devices.

The CMSIS is defined in close cooperation with various silicon and software vendors and provides a common approach to interface to peripherals, real-time operating systems, and middleware components. The CMSIS is intended to enable the combination of software components from multiple middleware vendors.

CMSIS Version 5 supports also the Armv8-M architecture including TrustZone® for Armv8-M hardware security extensions and the Cortex-M23 and Cortex-M33 processors.

CMSIS has been created to help the industry in standardization. It enables consistent software layers and device support across a wide range of development tools and microcontrollers. CMSIS is not a huge software layer that introduces overhead and does not define standard peripherals. The silicon industry can therefore support the wide variations of Cortex-M processor-based devices with this common standard.

In detail the benefits of the CMSIS are:

The CMSIS uses the following essential coding rules and conventions:

In addition, the CMSIS recommends the following conventions for identifiers:

The CMSIS is documented within the source files with:

Doxygen comment example:

/** * @brief Enable Interrupt in NVIC Interrupt Controller * @param IRQn interrupt number that specifies the interrupt * @return none. * Enable the specified interrupt in the NVIC Interrupt Controller. * Other settings of the interrupt such as priority are not affected. */

The various components of CMSIS Version 5 are validated using mainstream compilers. To get a diverse coverage, Arm uses the Arm Compiler v5 (based on EDG front-end), the Arm Compiler v6 (based on LLVM front-end), and the GCC Compiler in the various tests. For each component, the section "Validation" describes the scope of the various verifications.

CMSIS components are compatible with a range of C and C++ language standards. The CMSIS components comply with the Application Binary Interface (ABI) for the Arm Architecture (exception CMSIS-RTOS v1). This ensures C API interfaces that support inter-operation between various toolchains.

As CMSIS defines API interfaces and functions that scale to a wide range of processors and devices, the scope of the run-time test coverage is limited. However, several components are validated using dedicated test suites.

The CMSIS source code is checked for MISRA C:2012 conformance using PC-Lint. MISRA deviations are documented with reasonable effort, however Arm does not claim MISRA compliance as there is today for example no guideline enforcement plan. The CMSIS source code is not checked for MISRA C++:2008 conformance as there is a risk that it is incompatible with C language standards, specifically warnings that may be generated by the various C compilers.

The CMSIS is provided free of charge by Arm under Apache 2.0 license. View the Apache 2.0 License.

The ARM::CMSIS Pack contains the following:

| File/Directory | Content |

|---|---|

| ARM.CMSIS.pdsc | Package description file in CMSIS-Pack format. |

| LICENSE.txt | CMSIS License Agreement (Apache 2.0) |

| CMSIS | CMSIS components (see below) |

| Device | CMSIS reference implementations of Arm Cortex-M processor based devices |

| Directory | Content |

|---|---|

| Documentation | This documentation |

| Core | User code templates for CMSIS-Core (Cortex-M) related files, referenced in ARM.CMSIS.PDSC |

| Core_A | User code templates for CMSIS-Core (Cortex-A) related files, referenced in ARM.CMSIS.PDSC |

| DAP | CMSIS-DAP Debug Access Port source code and reference implementations |

| Driver | Header files for the CMSIS-Driver peripheral interface API |

| DSP_Lib | CMSIS-DSP software library source code |

| NN | CMSIS-NN software library source code |

| Include | Include files for CMSIS-Core (Cortex-M) and CMSIS-DSP |

| Lib | CMSIS-DSP generated libraries for ARMCC and GCC |

| Pack | CMSIS-Pack example |

| RTOS | CMSIS-RTOS Version 1 along with RTX reference implementation |

| RTOS2 | CMSIS-RTOS Version 2 along with RTX reference implementation |

| SVD | CMSIS-SVD example |

| Utilities | PACK.xsd (CMSIS-Pack schema file), PackChk.exe (checking tool for software packs), CMSIS-SVD.xsd (CMSIS-SVD schema file), SVDConv.exe (conversion tool for SVD files) |