# XST User Guide for Virtex-6, Spartan-6, and 7 Series Devices

UG687 (v 14.5) March 20, 2013

This document applies to the following software versions: ISE Design Suite 14.5 and 14.6

#### Notice of Disclaimer

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials or to notify you of updates to the Materials or to product specifications. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at http://www.xilinx.com/warranty.htm; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: http://www.xilinx.com/warranty.htm#critapps.

© Copyright 2002-2013 Xilinx Inc. All rights reserved. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. The PowerPC name and logo are registered trademarks of IBM Corp., and used under license. All other trademarks are the property of their respective owners.

| Date       | Version |                                                                                                                                         |  |

|------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| 10/16/2012 | 14.3    | Made the following changes for various CRs:                                                                                             |  |

|            |         | • Added warning to Run Command section about the use of multiple run commands.                                                          |  |

|            |         | • Replaced code in Log2 function in HDL Coding Techniques chapter.                                                                      |  |

|            |         | • Added note to Asymmetric Ports Support (Block RAM) section warning that data buses larger than 18-bits will require a RAMB36E1 block. |  |

|            |         | • Removed sections about VHDL floating point and real math packages.                                                                    |  |

## **Revision History**

# Table of Contents

| Revision History2                                    |

|------------------------------------------------------|

| Chapter 1 Introduction9                              |

| Architecture Support9                                |

| Coding Examples9                                     |

| Syntax Examples9                                     |

| Acronyms9                                            |

| Additional Resources10                               |

| Chapter 2 Creating and Synthesizing an XST Project11 |

| Creating an HDL Synthesis Project File11             |

| Running XST in ISE Design Suite13                    |

| Running XST in Command Line Mode13                   |

| Chapter 3 VHDL Support23                             |

| VHDL IEEE Support23                                  |

| VHDL Data Types24                                    |

| VHDL Objects                                         |

| VHDL Operators                                       |

| VHDL Entity and Architecture Descriptions32          |

| VHDL Combinatorial Circuits                          |

| VHDL Sequential Logic51                              |

| VHDL Functions and Procedures57                      |

| VHDL Assert Statements60                             |

| VHDL Libraries and Packages63                        |

| VHDL File Type Support66                             |

| VHDL Constructs71                                    |

| VHDL Reserved Words75                                |

| Chapter 4 Verilog Support77                          |

| Verilog Design77                                     |

| Verilog Functionality78                              |

| More Information78                                   |

| Verilog–2001 Support79                               |

| Verilog Variable Part Selects80                      |

| Structural Verilog                                   |

| Verilog Parameters                                   |

| Verilog Parameter and Attribute Conflicts86          |

| Verilog Usage Restrictions87                     |

|--------------------------------------------------|

| Verilog–2001 Attributes and Meta Comments        |

| Verilog Constructs91                             |

| Verilog System Tasks and Functions94             |

| Verilog Primitives                               |

| Verilog User Defined Primitive (UDP)98           |

| Verilog Reserved Keywords101                     |

| Chapter 5 Behavioral Verilog103                  |

| Variables in Behavioral Verilog103               |

| Initial Values                                   |

| Arrays of Reg and Wire104                        |

| Multi-Dimensional Arrays104                      |

| Data Types                                       |

| Legal Statements                                 |

| Expressions                                      |

| Blocks                                           |

| Modules                                          |

| Continuous Assignments111                        |

| Procedural Assignments 112                       |

| Tasks and Functions119                           |

| Blocking and Non-Blocking Procedural Assignments |

| Constants                                        |

| Macros                                           |

| Include Files                                    |

| Behavioral Verilog Comments124                   |

| Generate Statements 124                          |

| Chapter 6 Mixed Language Support127              |

| Mixing VHDL and Verilog127                       |

| Instantiation127                                 |

| VHDL and Verilog Libraries127                    |

| VHDL and Verilog Boundary Rules128               |

| Generics Support130                              |

| Port Mapping131                                  |

| Library Search Order (LSO) Files132              |

| Chapter 7 HDL Coding Techniques137               |

| Advantages of VHDL137                            |

| Advantages of Verilog137                         |

| Macro Inference Flow Overview138                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------|

| Flip-Flops and Registers139                                                                                              |

| Latches143                                                                                                               |

| Tristates146                                                                                                             |

| Counters and Accumulators150                                                                                             |

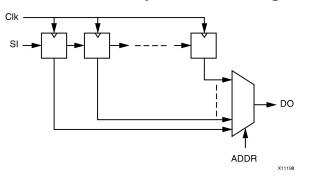

| Shift Registers154                                                                                                       |

| Dynamic Shift Registers163                                                                                               |

| Multiplexers                                                                                                             |

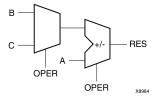

| Arithmetic Operators HDL Coding Techniques 172                                                                           |

| Comparators                                                                                                              |

| Dividers                                                                                                                 |

| Adders, Subtractors, and Adders/Subtractors                                                                              |

| Multipliers                                                                                                              |

| Multiply-Add and Multiply-Accumulate190                                                                                  |

| Extended DSP Inferencing 194                                                                                             |

| Resource Sharing197                                                                                                      |

| RAM HDL Coding Techniques200                                                                                             |

| ROM HDL Coding Techniques262                                                                                             |

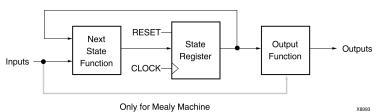

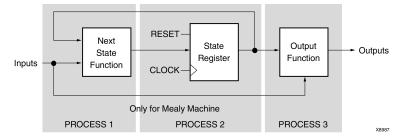

| FSM Components                                                                                                           |

| Black Boxes                                                                                                              |

| Chapter 8 FPGA Optimization                                                                                              |

| Mapping Logic to Block RAM285                                                                                            |

| Flip-Flop Implementation Guidelines                                                                                      |

| Flip-Flop Retiming                                                                                                       |

| Speed Optimization Under Area Constraint                                                                                 |

| Implementation Constraints                                                                                               |

| Device Primitive Support                                                                                                 |

| Using the UniMacro Library 297                                                                                           |

| Cores Processing                                                                                                         |

| Mapping Logic to LUTs                                                                                                    |

|                                                                                                                          |

| Controlling Placement on the Device                                                                                      |

| Controlling Placement on the Device                                                                                      |

| C C                                                                                                                      |

| Inserting Buffers                                                                                                        |

| Inserting Buffers       302         Using the PCI Flow With XST       302         Chapter 9 Design Constraints       305 |

| Inserting Buffers                                                                                                        |

| VHDL Attributes                       |

|---------------------------------------|

| Verilog-2001 Attributes 310           |

| XST Constraint File (XCF) 312         |

| Chapter 10 General Constraints        |

| Add I/O Buffers                       |

| Box Type                              |

| Bus Delimiter                         |

| Case                                  |

| Case Implementation Style             |

| Duplication Suffix                    |

| Full Case 326                         |

| Generate RTL Schematic                |

| Generics                              |

| HDL Library Mapping File332           |

| Hierarchy Separator                   |

| Ignore Synthesis Constraints File 335 |

| I/O Standard                          |

| Keep                                  |

| Keep Hierarchy 339                    |

| Library Search Order                  |

| LOC                                   |

| Netlist Hierarchy                     |

| Optimization Effort                   |

| Optimization Goal                     |

| Parallel Case                         |

| RLOC                                  |

| Save                                  |

| Synthesis Constraint File             |

| Translate Off and Translate On        |

| Verilog Include Directories           |

| Verilog Macros                        |

| Work Directory                        |

| Chapter 11 HDL Constraints            |

| Automatic FSM Extraction              |

| Enumerated Encoding                   |

| Equivalent Register Removal           |

| FSM Encoding Algorithm                |

| Mux Minimal Size                             |

|----------------------------------------------|

| Resource Sharing                             |

| Safe Implementation                          |

| Safe Recovery State                          |

| Chapter 12 FPGA Constraints (Non-Timing)375  |

| Asynchronous to Synchronous                  |

| Automatic BRAM Packing                       |

| BRAM Read-First Implementation               |

| BRAM Utilization Ratio                       |

| Buffer Type 383                              |

| Convert Tristates to Logic                   |

| Cores Search Directories                     |

| DSP Utilization Ratio                        |

| Extract BUFGCE                               |

| FSM Style                                    |

| LUT Combining                                |

| Map Entity on a Single LUT                   |

| Map Logic on BRAM                            |

| Max Fanout                                   |

| Move First Stage                             |

| Move Last Stage 402                          |

| Multiplier Style                             |

| Number of Global Clock Buffers               |

| Optimize Instantiated Primitives 402         |

| Pack I/O Registers Into IOBs 409             |

| Power Reduction                              |

| RAM Extraction                               |

| RAM Style                                    |

| Read Cores                                   |

| Reduce Control Sets                          |

| Register Balancing 420                       |

| Register Duplication                         |

| ROM Extraction                               |

| ROM Style                                    |

| Shift Register Extraction                    |

| Shift Register Minimum Size                  |

| Slice (LUT-FF Pairs) Utilization Ratio       |

| Slice (LUT-FF Pairs) Utilization Ratio Delta |

| (                                            |

| Use Carry Chain                            |

|--------------------------------------------|

| Use Clock Enable                           |

| Use DSP Block                              |

| Use Low Skew Lines                         |

| Use Synchronous Set                        |

| Use Synchronous Reset                      |

| Chapter 13 Timing Constraints              |

| Applying Timing Constraints 449            |

| Clock Signal 451                           |

| Cross Clock Analysis                       |

| From-To                                    |

| Global Optimization Goal454                |

| Offset                                     |

| Period                                     |

| Timing Name                                |

| Timing Name on a Net                       |

| Timegroup                                  |

| Timing Ignore                              |

| Write Timing Constraints 462               |

| Chapter 14 Third-Party Constraints463      |

| Third-Party Constraints in VHDL            |

| Third-Party Constraints in Verilog         |

| XST Equivalents to Third-Party Constraints |

| Chapter 15 Synthesis Report469             |

| Synthesis Report Content                   |

| Synthesis Report Navigation                |

| Synthesis Report Information               |

| Chapter 16 Naming Conventions479           |

| Naming Conventions Coding Examples         |

| Net Naming Conventions                     |

| Instance Naming Conventions                |

| Case Preservation                          |

| Name Generation Control 484                |

| Appendix Additional Resources              |

## Chapter 1

## Introduction

## **Architecture Support**

This Guide applies to Xilinx® Virtex®-6, Spartan®-6, and 7 series devices. All features and constraints in this Guide support those devices, except as noted. For information on other devices, see the *XST User Guide for Virtex-4*, *Virtex-5*, *Spartan-3*, *and Newer CPLD Devices (UG627)*.

## **Coding Examples**

The coding examples in this Guide are accurate as of the date of publication. Where indicated within the coding example, you can download updates and other examples from http://www.xilinx.com/txpatches/pub/documentation/misc/xstug\_examples.zip. Each directory contains a summary.txt file listing all examples, together with a brief overview.

## Syntax Examples

The syntax examples in this Guide show how to specify constraints with particular tools or methods, including, where applicable, VHDL, Verilog, User Constraints File (UCF), XST Constraint File (XCF), ISE® Design Suite, and the Command Line. Not all constraints can be specified with all tools or methods. If a tool or method is not listed for that constraint, you cannot use the constraint with it.

## Acronyms

| Acronym | Meaning                             |  |

|---------|-------------------------------------|--|

| HDL     | Hardware Description Language       |  |

| VHDL    | VHSIC Hardware Description Language |  |

| RTL     | Register Transfer Level             |  |

| LRM     | Language Reference Manual           |  |

| FSM     | Finite State Machine                |  |

| EDIF    | Electronic Data Interchange Format  |  |

| LSO     | Library Search Order                |  |

| XST     | Xilinx® Synthesis Technology (XST)  |  |

| XCF     | XST Constraint File                 |  |

## **Additional Resources**

For more information about XST, and for references to further documentation, see Additional Resources at the end of this Guide.

## Chapter 2

# Creating and Synthesizing an XST Project

The Xilinx® Synthesis Technology (XST) software:

- Is the Xilinx® proprietary logic synthesis solution.

- Is available in:

- ISE® Design Suite

- The PlanAhead<sup>™</sup> software

- Can run as a standalone tool in command line mode.

The XST software:

- 1. Takes the description of a design in an HDL (VHDL or Verilog) file.

- 2. Converts it to a synthesized netlist of Xilinx technology-specific logical resources.

- 3. The synthesized netlist, representing a logical view of the design, is then:

- a. Processed by the design implementation tool chain.

- b. Converted into a physical representation.

- c. Converted to a bitstream file to program Xilinx devices.

## Creating an HDL Synthesis Project File

XST separates 1) information about the design, from 2) information about how XST should process the design.

| File                       | Contains                     |

|----------------------------|------------------------------|

| HDL synthesis project file | Information about the design |

| XST script file            | Synthesis parameters         |

## **HDL Synthesis Project File Definition**

An HDL synthesis project file:

- Is an ASCII text file.

- Lists the HDL source files that make up the design.

- Specifies a separate HDL source file on each line.

- Usually has a .prj extension.

## HDL Synthesis Project File Syntax

<hdl\_language> <compilation\_library> <source\_file>

- hdl\_language

- Specifies whether the designated HDL source file is written in VHDL or Verilog.

- Allows you to create mixed VHDL and Verilog language projects.

- compilation\_library

- Specifies the logic library in which the HDL is compiled.

- The default logic library is work.

- source\_file

- Specifies the HDL source file.

- Uses an absolute or a relative path.

- A relative path is relative to the location of the HDL synthesis project file.

## Creating a Sample HDL Synthesis Project File in ISE Design Suite

To create a sample HDL synthesis project file in ISE® Design Suite:

1. Run the following code:

| vhdl    | work        | my_vhdl1.vhd                  |

|---------|-------------|-------------------------------|

| verilog | work        | my_vlg1.v                     |

| vhdl    | my_vhdl_lib | /my_other_srcdir/my_vhdl2.vhd |

| verilog | my_vlg_lib  | my_vlg2.v                     |

| verriog | my_v19_110  | my_v192.v                     |

The code uses relative paths.

- 2. XST creates an HDL synthesis project file in the project directory. The file has a.prj extension.

- 3. XST adds entries to the HDL synthesis project file whenever you add an HDL source file to the project.

For more information, see the ISE Design Suite Help.

## Creating an HDL Synthesis Project File from the Command Line

To create an HDL synthesis project file from the command line:

- 1. Create the HDL synthesis project file manually.

- Enter an Input File Name (-ifn) switch on the run command line.

The -ifn switch tells XST the location of the HDL synthesis project file.

## **Running XST in ISE Design Suite**

To run XST in ISE® Design Suite:

1. Create a new project.

File > New Project

2. Import HDL source files.

**Project > Add Copy of Source**

3. Select the top-level block.

### Design > Hierarchy

- 4. If ISE Design Suite did not select the correct block as the top-level block:

- a. Select the correct block.

- b. Right-click Select Set as Top Module.

- c. Right-click **Processes > Synthesize-XST.**

- 5. To view all available synthesis options, select Process > Properties.

- 6. To start synthesis:

- a. Right-click.

- b. Select Run.

For more information, see the ISE Design Suite Help.

## **Running XST in Command Line Mode**

You can run XST in command line mode, which includes:

- Running XST as a Standalone Tool

- Running XST Interactively

- Running XST in Scripted Mode

## **Running XST as a Standalone Tool**

XST can run as a standalone tool.

In command line mode, XST runs as part of a scripted design implementation, not in the ISE® Design Suite graphical user interface (GUI).

### **Setting Environment Variables**

Before running XST, set the following environment variables to point to the correct installation directory. This example is for 64-bit Linux.

setenv XILINX setenv PATH \$XILINX/bin/lin64:\$PATH

setenv LD\_LIBRARY\_PATH \$XILINX/lib/lin64:\$LD\_LIBRARY\_PATH

### Invoking XST

| Operating System | Command |

|------------------|---------|

| Windows          | xst.exe |

| Linux            | xst     |

### **Command Line Syntax**

```

xst[.exe] [-ifn in_file_name] [-ofn out_file_name] [-intstyle]

[-filter msgfilter_file_name]

```

• –ifn

Designates the XST script file containing the commands to execute.

- If **–ifn** is omitted, XST runs interactively.

- If **-ifn** is specified, XST runs in scripted mode.

- –ofn

Forces redirection of the XST log to a directory and file of your choice. The XST log is written to an SRP file in the work directory.

-intstyle

Controls reporting on the standard output. For more information, see Silent Mode.

-filter

Enables limited message filtering in command line mode.

### Using Message Filtering in Command Line Mode

To use message filtering in command line mode:

- 1. Synthesize your design once in command line mode without any message filtering.

- 2. Run the Xilinx® **xreport** tool:

xreport -config example.xreport -reports\_dir . -filter

example.filter example &

- The directory defined by **-reports\_dir** should be the same directory in which the XST log file was created.

- The above example assumes that:

- The log file generated from the initial run is named example.srp.

- The log file is located in the same directory in which XST was invoked.

For more information, run **xreport** –**h**.

- 3. Select **Design Overview > Summary**.

- 4. Select Design Properties > Enable Message Filtering.

- 5. Select **Design Overview > Synthesis Messages** to display messages from the XST log file.

- 6. Select the messages to be filtered.

- 7. Right click.

- 8. Select either **Filter All Instances of This Message**, or **Filter This Instance Only** The message filter configuration is saved in the file example.filter.

- 9. Run XST again in command line mode using the **–filter** switch:

xst ... -filter example.filter ...

For more advanced filtering, or to re-enable previously disabled messages:

- 1. Right click in the **Synthesis Messages** pane.

- 2. Select Edit Message Filters.

### **Running XST Interactively**

- Run XST without **-ifn** to enter instructions on the command line.

- The -ifn option has no effect in interactive mode, since no XST log file is created.

## **Running XST in Scripted Mode**

- Instead of entering commands at the command prompt, create an XST script file containing the commands and options.

- When you run XST in a scripted implementation flow, you must:

- Manually create an XST script file in advance, or

- Generate the XST script file on the fly.

### **XST Script Files**

An XST script file:

- Is an ASCII text file.

- Contains one or more XST commands.

- Is passed to XST by -ifn.

- xst -ifn myscript.xst

- Has no mandatory file extension. ISE® Design Suite creates XST script files with an .xst extension.

## Improving Readability of an XST Script File

- Each option-value pair is on a separate line.

- The first line contains only the **run** command without any options.

- There are no blank lines in the middle of the command.

- Each line containing an option-value pair begins with a dash.

- Each option has one value.

- There are no options without a value.

- The value for a given option can be:

- Predefined by XST (for example, yes or no)

- An integer

- Any string, such as a file name or a name of the top level entity

- Options such as **-vlgincdir** accept multiple directories as values.

- Separate the directory names with spaces.

For more information, see Names With Spaces in Command Line Mode.

• Enclose the directory list in {braces}.

-vlgincdir {c:\vlg1 c:\vlg2}

- Use the pound (#) character to:

- Comment out options.

- Place additional comments in the script file.

### **Example XST Script File**

```

run

-ifn myproject.prj

-ofn myproject.ngc

-ofmt NGC

-p virtex6

# -opt_mode area

-opt_mode speed

-opt_level 1

```

## **XST Commands**

XST recognizes the following commands:

- Run Command

- Set Command

- Help Command

### **Run Command**

The run command:

- Is the main synthesis command.

- Is used only once per script file.

- Runs synthesis in its entirety.

- Synthesis begins by parsing the HDL source files.

- Synthesis ends by generating the final netlist.

- Runs HDL Parsing and Elaboration in order to:

- Verify language compliance, or

- Pre-compile HDL files.

**Note** Xilinx does not support or recommend the use of multiple run commands in a single script.

### **Run Command Syntax**

run option\_1 value option\_2 value ...

- The **run** command is not case sensitive, except for option values that designate elements of the HDL description, such as the top-level module.

- You can specify an option in either lowercase or uppercase. For example, options **yes** and **YES** are treated identically.

### **Run Command Settings**

The following tables list mandatory and optional settings for the **run** command. For additional options in command line mode, see:

- Chapter 10, XST General Constraints

- Chapter 11, XST HDL Constraints

- Chapter 12, XST FPGA Constraints (Non-Timing)

- Chapter 13, XST Timing Constraints

| Option              | Command Line<br>Name | Option Value                                                                                                                       | Note                                                                                                                                                                                               |

|---------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input File<br>Name  | -ifn                 | Relative or absolute path to an HDL Synthesis Project file                                                                         |                                                                                                                                                                                                    |

| Output File<br>Name | -ofn                 | Relative or absolute path to a file in which the post-synthesis NGC netlist is saved.                                              | You may omit the .ngc extension.                                                                                                                                                                   |

| Target<br>Device    | -р                   | <ul> <li>A specific device, such as xc6vlx240t-ff1759-1, or</li> <li>A generic device family, such as Virtex®-6 devices</li> </ul> |                                                                                                                                                                                                    |

| Top Module<br>Name  | -top                 | Name of the VHDL entity or Verilog module describing<br>the top level of your design.                                              | If you are using<br>a separate VHDL<br>configuration declaration<br>to bind component<br>instantiations to design<br>entities and architectures,<br>the value is the name of<br>the configuration. |

### **Run Command Mandatory Settings**

| Option                                                                                                                                                                                         | Command Line Name         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| VHDL Top Level Architecture (Name of the specific<br>VHDL architecture to be tied to the top level VHDL entity.<br>Not applicable if the top level of your design is described<br>in Verilog.) | -ent                      |

| Optimization Goal                                                                                                                                                                              | -opt_mode                 |

| Optimization Effort                                                                                                                                                                            | -opt_level                |

| Power Reduction                                                                                                                                                                                | -power                    |

| Use Synthesis Constraints File                                                                                                                                                                 | -iuc                      |

| Synthesis Constraints File                                                                                                                                                                     | -uc                       |

| Keep Hierarchy                                                                                                                                                                                 | -keep_hierarchy           |

| Netlist Hierarchy                                                                                                                                                                              | -netlist_hierarchy        |

| Global Optimization Goal                                                                                                                                                                       | -glob_opt                 |

| Generate RTL Schematic                                                                                                                                                                         | -rtlview                  |

| Read Cores                                                                                                                                                                                     | -read_cores               |

| Cores Search Directories                                                                                                                                                                       | -sd                       |

| Write Timing Constraints                                                                                                                                                                       | -write_timing_constraints |

| Cross Clock Analysis                                                                                                                                                                           | -cross_clock_analysis     |

| Hierarchy Separator                                                                                                                                                                            | -hierarchy_separator      |

| Bus Delimiter                                                                                                                                                                                  | -bus_delimiter            |

| LUT-FF Pairs Utilization Ratio                                                                                                                                                                 | -slice_utilization_ratio  |

| BRAM Utilization Ratio                                                                                                                                                                         | -bram_utilization_ratio   |

| DSP Utilization Ratio                                                                                                                                                                          | -dsp_utilization_ratio    |

| Case                                                                                                                                                                                           | -case                     |

| Library Search Order                                                                                                                                                                           | -lso                      |

| Verilog Include Directories                                                                                                                                                                    | -vlgincdir                |

| Generics                                                                                                                                                                                       | -generics                 |

| Verilog Macros                                                                                                                                                                                 | -define                   |

| FSM Extraction                                                                                                                                                                                 | -fsm_extract              |

| FSM Encoding Algorithm                                                                                                                                                                         | -fsm_encoding             |

| Safe Implementation                                                                                                                                                                            | -safe_implementation      |

| Case Implementation Style                                                                                                                                                                      | -vlgcase                  |

| FSM Style                                                                                                                                                                                      | -fsm_style                |

| RAM Extraction                                                                                                                                                                                 | -ram_extract              |

| RAM Style                                                                                                                                                                                      | -ram_style                |

| ROM Extraction                                                                                                                                                                                 | -rom_extract              |

| ROM Style                                                                                                                                                                                      | -rom_style                |

| Automatic BRAM Packing                                                                                                                                                                         | -auto_bram_packing        |

| Shift Register Extraction                                                                                                                                                                      | -shreg_extract            |

### **Run Command Optional Settings**

| Option                           | Command Line Name            |

|----------------------------------|------------------------------|

| Shift Register Minimum Size      | -shreg_min_size              |

| Resource Sharing                 | -resource_sharing            |

| Use DSP Block                    | -use_dsp48                   |

| Asynchronous To Synchronous      | -async_to_sync               |

| Add I/O Buffers                  | -iobuf                       |

| Max Fanout                       | -max_fanout                  |

| Number of Clock Buffers          | -bufg                        |

| Register Duplication             | -register_duplication        |

| Equivalent Register Removal      | -equivalent_register_removal |

| Register Balancing               | -register_balancing          |

| Move First Flip-Flop Stage       | -move_first_stage            |

| Move Last Flip-Flop Stage        | -move_last_stage             |

| Pack I/O Registers into IOBs     | -iob                         |

| LUT Combining                    | -lc                          |

| Reduce Control Sets              | -reduce_control_sets         |

| Use Clock Enable                 | -use_clock_enable            |

| Use Synchronous Set              | -use_sync_set                |

| Use Synchronous Reset            | -use_sync_reset              |

| Optimize Instantiated Primitives | -optimize_primitives         |

### Set Command

Set preferences with the set command before invoking the run command.

set -option\_name [option\_value]

For more information, see Chapter 9, Design Constraints.

| Option     | Description                                                                 | Values                        |

|------------|-----------------------------------------------------------------------------|-------------------------------|

| -tmpdir    | Location of all temporary files<br>generated by XST during a<br>session     | Any valid path to a directory |

| -xsthdpdir | Work Directory (location of<br>all files resulting from HDL<br>compilation) | Any valid path to a directory |

| -xsthdpini | HDL Library Mapping File<br>(INI file)                                      | file_name                     |

### **Help Command**

Use the **help** command to view:

- Supported families

- All commands for a specific device

- Specific commands for a specific device

### **Supported Families**

To see a list of supported families:

1. Type **help** at the command line with no argument.

help

2. XST issues a message:

```

--> help ERROR:Xst:1356 - Help : Missing "-arch ". Please

specify what family you want to target available families:

spartan6 virtex6

```

3. A list of supported families follows available families.

### All Commands for a Specific Device

To see all commands for a specific device:

1. Type the following at the command line:

help -arch family\_name

*family\_name* is a supported device family.

2. For example, to see all commands for Virtex®-6 devices, type:

```

help -arch virtex6

```

### **Specific Commands for a Specific Device**

To see information about a specific command for a specific device:

- 1. Type the following at the command line

- help -arch family\_name -command command\_name

- *family\_name* is a supported device family

- *command\_name* is one of the following commands:

- run

- set

- time

- 2. For example, to see information about the run command for Virtex-6 devices, type:

help -arch virtex6 -command run

### Names With Spaces in Command Line Mode

XST supports file and directory names with spaces in command line mode.

Enclose file and directory names with spaces in double quotes:

"C:\my project"

• For options supporting multiple directories (**-sd** and **-vlgincdir**), enclose multiple directories in {braces}.

-vlgincdir {"C:\my project" C:\temp}

• In earlier releases of XST, multiple directories were enclosed in double quotes. XST still supports this syntax, provided that the directory names do not contain spaces. Xilinx® recommends that you change existing scripts to the new syntax enclosing multiple directories in {braces}.

### **Output Files**

XST output files include:

- Typical Output Files

- Temporary Output Files

### **Typical Output Files**

XST generates the following typical output files:

- Output NGC netlist (NGC) (.ngc)

- In ISE® Design Suite, the NGC file is created in the project directory.

- In command line mode, the NGC file is created in:

- The current directory, or

- Any other directory specified by **run -ofn**.

- Register Transfer Level (RTL) netlist for the RTL Viewer (NGR) (.ngr)

- Synthesis log file (SRP) (.srp)

### **Temporary Output Files**

- XST generates temporary files in the XST TEMP (temp) directory.

- HDL compilation files are generated in the TEMP directory.

- The default TEMP directory is the XST subdirectory of the current directory.

### **Temp Directory Locations**

| System       | Location                                                                             |

|--------------|--------------------------------------------------------------------------------------|

| Workstations | /tmp                                                                                 |

| Windows      | The directory specified by either the <i>TEMP</i> or <i>TMP</i> environment variable |

### **Changing the Temp Directory**

To change the TEMP directory, run **set** -tmpdir <directory>:

- At the XST prompt, or

- In an XST script file.

### **Maintaining the Temp Directory**

- The TEMP directory contains the files resulting from the compilation of all VHDL and Verilog files during all XST sessions.

- The number of files stored in the TEMP directory can severely impact CPU performance.

- XST does not automatically clean the TEMP directory. Xilinx® recommends that you manually clean the TEMP directory on a regular basis.

## Chapter 3

## VHDL Support

XST supports the VHSIC Hardware Description Language (VHDL) except as otherwise noted.

- VHDL compactly describes complicated logic.

- VHDL allows you to:

- Describe the structure of a system:

- How the system is decomposed into subsystems.

- How those subsystems are interconnected.

- Specify the function of a system using familiar programming language forms.

- Simulate a system design before it is implemented and programmed in hardware.

- Produce a detailed, device-dependent version of a design to be synthesized from a more abstract specification.

For more information, see:

- IEEE VHDL Language Reference Manual (LRM)

- Chapter 9, Design Constraints, especially VHDL Attributes

## VHDL IEEE Support

The XST parsing and elaboration engine complies with VHDL IEEE 1076-1993.

XST supports non-LRM compliant constructs when the construct:

- Is supported by most synthesis and simulation tools.

- Greatly simplifies coding.

- Does not cause negatively impact synthesis.

- Does not negatively impact quality of results.

#### Non-LRM Compliant Example

- The LRM does not allow instantiation with a port map if:

- A formal port is a buffer, and

- The corresponding effective port is an **out**.

- XST supports this non-LRM compliant construct. The construct meets the criteria stated above in XST Support for Non-LRM Compliant Constructs.

## **VHDL Data Types**

Some VHDL data types are part of predefined packages.

For information on where they are compiled, and how to load them, see VHDL Predefined Packages.

## **VHDL Unsupported Data Types**

VHDL supports the **real** type defined in the standard package for calculations only, such as the calculation of generics values.

You cannot define a synthesizable object of type real.

## VHDL Data Types

VHDL data types include:

- VHDL Predefined Enumerated Types

- VHDL User-Defined Enumerated Types

- VHDL Bit Vector Types

- VHDL Integer Types

- VHDL Multi-Dimensional Array Types

- VHDL Record Types

### **VHDL Predefined Enumerated Types**

XST supports the following predefined VHDL enumerated types for hardware description:

- The **bit** type, defined in the standard package.

- Allowed values are **0** (logic zero) and **1** (logic 1).

- The **boolean** type, defined in the standard package.

Allowed values are **false** and **true**.

• The type defined in the IEEE **std\_logic\_1164** package.

For allowed values, see the *std\_logic Allowed Values* table below.

This information is summarized in the following table.

### Predefined VHDL Enumerated Types Summary

| Enumerated Type | Defined In                  | Allowed Values                                       |

|-----------------|-----------------------------|------------------------------------------------------|

| bit             | standard package            | • 0 (logic zero)                                     |

|                 |                             | • 1 (logic 1)                                        |

| boolean         | standard package            | • false                                              |

|                 |                             | • true                                               |

| std_logic       | IEEE std_logic_1164 package | See the <i>std_logic Allowed Values</i> table below. |

| Value | Meaning        | What XST does                   |

|-------|----------------|---------------------------------|

| U     | unitialized    | Not accepted by XST             |

| Х     | unknown        | Treated as don't care           |

| 0     | low            | Treated as logic zero           |

| 1     | high           | Treated as logic one            |

| Z     | high impedance | Treated as high impedance       |

| W     | weak unknown   | Not accepted by XST             |

| L     | weak low       | Treated identically to <b>0</b> |

| Н     | weak high      | Treated identically to 1        |

| -     | don't care     | Treated as don't care           |

### std\_logic Allowed Values

### XST-Supported Overloaded Enumerated Types

| Туре       | Defined In IEEE<br>Package | SubType Of | Contains Values                                       |

|------------|----------------------------|------------|-------------------------------------------------------|

| std_ulogic | std_logic_1164             | N/A        | <ul> <li>Same nine values<br/>as std_logic</li> </ul> |

|            |                            |            | • Does not contain predefined resolution functions    |

| X01        | std_logic_1164             | std_ulogic | X, 0, 1                                               |

| X01Z       | std_logic_1164             | std_ulogic | X, 0, 1, Z                                            |

| UX01       | std_logic_1164             | std_ulogic | U, X, 0 1                                             |

| UX01Z      | std_logic_1164             | std_ulogic | U, X, 0, Z                                            |

### **VHDL User-Defined Enumerated Types**

You can create your own enumerated types.

User-defined enumerated types usually describe the states of a Finite State Machine (FSM).

### VHDL User-Defined Enumerated Types Coding Example

type STATES is (START, IDLE, STATE1, STATE2, STATE3) ;

## VHDL Bit Vector Types

### Supported VHDL Bit Vector Types

| Туре             | Defined In Package  | Models                       |

|------------------|---------------------|------------------------------|

| bit_vector       | Standard            | Vector of bit elements       |

| std_logic_vector | IEEE std_logic_1164 | Vector of std_logic elements |

### Supported VHDL Overloaded Types

| Туре              | Defined In IEEE Package |  |

|-------------------|-------------------------|--|

| std_ulogic_vector | std_logic_1164          |  |

| unsigned          | std_logic_arith         |  |

| signed            | std_logic_arith         |  |

### **VHDL Integer Types**

The integer type is a predefined VHDL type.

- XST implements an integer on 32 bits by default.

- For a more compact implementation, define the exact range of applicable values.

type MSB is range 8 to 15

• You can also take advantage of the predefined natural and positive types, overloading the integer type.

## **VHDL Multi-Dimensional Array Types**

XST supports VHDL multi-dimensional array types.

- Although there is no restriction on the number of dimensions, Xilinx® recommends that you describe no more than three dimensions.

- Objects of multi-dimensional array type that you can describe are:

- Signals

- Constants

- Variables

- Objects of multi-dimensional array type can be:

- Passed to functions.

- Used in component instantiations.

### Fully Constrained Array Type Coding Example

An array type must be fully constrained in all dimensions.

subtype WORD8 is STD\_LOGIC\_VECTOR (7 downto 0); type TAB12 is array (11 downto 0) of WORD8; type TAB03 is array (2 downto 0) of TAB12;

### Array Declared as a Matrix Coding Example

You can declare an array as a matrix.

subtype TAB13 is array (7 downto 0,4 downto 0) of STD\_LOGIC\_VECTOR (8 downto 0);

#### Multi-Dimensional Array Signals and Variables Coding Examples

These coding examples demonstrate the uses of multi-dimensional array signals and variables in assignments.

1. Make the following declarations:

- 2. You can now specify:

- A multi-dimensional array signal or variable

```

TAB_A <= TAB_B; TAB_C <= TAB_D; TAB_C <= CNST_A;

```

• An index of one array

TAB\_A (5) <= WORD\_A; TAB\_C (1) <= TAB\_A;</pre>

• Indexes of the maximum number of dimensions

TAB\_A (5) (0) <= '1'; TAB\_C (2) (5) (0) <= '0'

A slice of the first array

TAB\_A (4 downto 1) <= TAB\_B (3 downto 0);</pre>

• An index of a higher level array and a slice of a lower level array

```

TAB_C (2) (5) (3 downto 0) <= TAB_B (3) (4 downto 1); TAB_D (0) (4) (2 downto 0)

\\ <= CNST_A (5 downto 3)

```

#### 3. Add the following declaration:

```

subtype MATRIX15 is array(4 downto 0, 2 downto 0) of STD_LOGIC_VECTOR (7 downto 0);

signal MATRIX_A : MATRIX15;

```

- 4. You can now specify:

- A multi-dimensional array signal or variable

MATRIXA <= CNST\_A

An index of one row of the array

MATRIXA (5) <= TAB\_A;

Indexes of the maximum number of dimensions

MATRIXA (5,0) (0) <= '1';

Indexes can be variable.

## **VHDL Record Types**

```

type mytype is record

field1 : std_logic;

field2 : std_logic_vector (3 downto 0)

end record;

```

- A field of a record type can also be of type **record**.

- Constants can be record types.

- Record types cannot contain attributes.

- XST supports aggregate assignments to record signals.

## **VHDL Objects**

VHDL objects include:

- VHDL Signals

- VHDL Variables

- VHDL Constants

## **VHDL Signals**

Declare a VHDL signal in:

• An architecture declarative part

Use the VHDL signal anywhere within that architecture.

A block

Use the VHDL signal within that block.

Assign the VHDL signal with the <= signal assignment operator.

signal sig1 : std\_logic; sig1 <= '1';</pre>

## **VHDL Variables**

A VHDL variable is:

- Declared in a process or a subprogram.

- Used within that process or subprogram.

- Assigned with the := assignment operator.

```

variable var1 : std_logic_vector (7 downto 0); var1 := "01010011";

```

## **VHDL Constants**

You can declare a VHDL constant in any declarative region.

- The constant is used within that region.

- The constant values cannot be changed once declared.

```

signal sig1 : std_logic_vector (5 downto 0);constant init0 :

std_logic_vector (5 downto 0) := "010111";sig1 <= init0;</pre>

```

## **VHDL Operators**

XST supports VHDL operators. See VHDL Operators Support.

## **Shift Operator Examples**

| Operator                     | Example                     | Logically Equivalent To                 |

|------------------------------|-----------------------------|-----------------------------------------|

| SLL (Shift Left Logic)       | sig1 <= A(4 downto 0) sll 2 | sig1 <= A(2 downto 0) & "00";           |

| SRL (Shift Right Logic)      | sig1 <= A(4 downto 0) srl 2 | sig1 <= "00" & A(4 downto 2);           |

| SLA (Shift Left Arithmetic)  | sig1 <= A(4 downto 0) sla 2 | sig1 <= A(2 downto 0) & A(0) & A(0);    |

| SRA (Shift Right Arithmetic) | sig1 <= A(4 downto 0) sra 2 | sig1 <= <= A(4) & A(4) & A(4 downto 2); |

| ROL (Rotate Left)            | sig1 <= A(4 downto 0) rol 2 | sig1 <= A(2 downto 0) & A(4 downto 3);  |

| ROR (Rotate Right)           | A(4 downto 0) ror 2         | sig1 <= A(1 downto 0) & A(4 downto 2);  |

## **VHDL Entity and Architecture Descriptions**

VHDL entity and architecture descriptions include:

- VHDL Circuit Descriptions

- VHDL Entity Declarations

- VHDL Architecture Declarations

- VHDL Component Instantiation

- VHDL Recursive Component Instantiation

- VHDL Component Configuration

- VHDL Generics

## **VHDL Circuit Descriptions**

A VHDL circuit description (design unit) consists of:

- Entity declaration

- Provides the *external* view of the circuit.

- Describes objects visible from the outside, including the circuit interface, such as the I/O ports and generics.

- Architecture

- Provides the *internal* view of the circuit.

- Describes the circuit behavior or structure.

## **VHDL Entity Declarations**

The I/O ports of the circuit are declared in the entity.

Each port has a:

- name

- mode

- in

- out

- inout

- buffer

- type

### **Constrained and Unconstrained Ports**

Ports can be constrained or unconstrained.

- Ports are usually constrained.

- Ports can be left unconstrained in the entity declaration.

- If ports are left unconstrained, their width is defined at instantiation when the connection is made between formal ports and actual signals.

- Unconstrained ports allow you to create different instantiations of the same entity, defining different port widths.

- Xilinx® recommends:

- Do not use unconstrained ports.

- Define ports that are constrained through generics.

- Apply different values of those generics at instantiation.

- Do not have an unconstrained port on the top-level entity.

- Array types of more than one-dimension are not accepted as ports.

- The entity declaration can also declare VHDL generics.

### **Buffer Port Mode**

Xilinx recommends that you not use buffer port mode.

- VHDL allows buffer port mode when a signal is used both:

- Internally, and

- As an output port when there is only one internal driver.

- Buffer ports:

- Are a potential source of errors during synthesis.

- Complicate validation of post-synthesis results through simulation.

#### NOT RECOMMENDED Coding Example WITH Buffer Port Mode

```

entity alu is

port(

CLK : in STD_LOGIC;

A : in STD_LOGIC_VECTOR(3 downto 0);

B : in STD_LOGIC_VECTOR(3 downto 0));

C : buffer STD_LOGIC_VECTOR(3 downto 0));

end alu;

architecture behavioral of alu is

begin

process begin

if rising_edge(CLK) then

C <= UNSIGNED(A) + UNSIGNED(B) UNSIGNED(C);

end if;

end process;

end behavioral;</pre>

```

### **Dropping Buffer Mode**

Xilinx recommends that you drop buffer port mode.

- In the coding example above, signal C:

- Has been modeled with a buffer mode.

- Is used both internally and as an output port.

- Every level of hierarchy that can be connected to C must also be declared as a buffer.

- To drop buffer mode:

- 1. Insert a dummy signal.

- 2. Declare port C as an output.

### **RECOMMENDED Coding Example WITHOUT Buffer Port Mode**

```

entity alu is

port(

CLK : in STD_LOGIC;

A : in STD_LOGIC_VECTOR(3 downto 0);

B : in STD_LOGIC_VECTOR(3 downto 0);

: out STD_LOGIC_VECTOR(3 downto 0));

С

end alu;

architecture behavioral of alu is

-- dummy signal

signal C_INT : STD_LOGIC_VECTOR(3 downto 0);

begin

C <= C_INT;

process begin

if rising_edge(CLK) then

C_INT <= A and B and C_INT;

end if;

end process;

end behavioral;

```

## **VHDL Architecture Declarations**

You can declare internal signals in the architecture.

Each internal signal has a:

- name

- type

### VHDL Architecture Declaration Coding Example

```

library IEEE;

use IEEE.std_logic_1164.all;

entity EXAMPLE is

port (

A,B,C : in std_logic;

D,E : out std_logic );

end EXAMPLE;

architecture ARCHI of EXAMPLE is

signal T : std_logic;

begin

...

end ARCHI;

```

## **VHDL Component Instantiation**

Component instantiation allows you to instantiate one design unit (component) inside another design unit in order to create a hierarchically structured design description.

To perform component instantiation:

- 1. Create the design unit (entity and architecture) modeling the functionality to be instantiated.

- 2. Declare the component to be instantiated in the declarative region of the parent design unit architecture.

- 3. Instantiate and connect this component in the architecture body of the parent design unit.

- 4. Map (connect) formal ports of the component to actual signals and ports of the parent design unit.

## **Elements of Component Instantiation Statement**

The main elements of a component instantiation statement are:

• Label

Identifies the instance.

- Association list

- Introduced by the reserved **port map** keyword.

- Ties formal ports of the component to actual signals or ports of the parent design unit.

- Optional association list

- Introduced by the reserved generic map keyword.

- Provides actual values to formal generics defined in the component.

XST supports unconstrained vectors in component declarations.

#### VHDL Component Instantiation Coding Example

This coding example shows the structural description of a half-Adder composed of four nand2 components.

```

-- A simple component instantiation example

Involves a component declaration and the component instantiation itself

_ _

_ _

-- Download: http://www.xilinx.com/txpatches/pub/documentation/misc/xstug_examples.zip

-- File: VHDL_Language_Support/instantiation/instantiation_simple.vhd

_ _

entity sub is

generic (

WIDTH : integer := 4);

port (

A,B : in BIT_VECTOR(WIDTH-1 downto 0);

: out BIT_VECTOR(2*WIDTH-1 downto 0));

0

end sub;

architecture archi of sub is

begin

0 <= A & B;

end ARCHI;

entity top is

generic (

WIDTH : integer := 2);

port (

X, Y : in BIT_VECTOR(WIDTH-1 downto 0);

Ζ

: out BIT_VECTOR(2*WIDTH-1 downto 0));

end top;

architecture ARCHI of top is

component sub -- component declaration

generic (

WIDTH : integer := 2);

port (

A,B : in BIT_VECTOR(WIDTH-1 downto 0);

0 : out BIT_VECTOR(2*WIDTH-1 downto 0));

end component;

begin

inst_sub : sub -- component instantiation

generic map (

WIDTH => WIDTH

)

port map (

A => X,

```

```

end ARCHI;

```

);

B => Y, O => Z

# **VHDL Recursive Component Instantiation**

XST supports VHDL recursive component instantiation.

- XST does not support direct instantiation for recursion.

- To prevent endless recursive calls, the number of recursions is limited by default to 64.

- Use **-recursion\_iteration\_limit** to specify the number of allowed recursive calls. See the following coding example.

#### VHDL Recursive Component Instantiation Coding Example

```

-- Recursive component instantiation

_ _

-- Download: http://www.xilinx.com/txpatches/pub/documentation/misc/xstug_examples.zip

-- File: VHDL_Language_Support/instantiation/instantiation_recursive.vhd

library ieee;

use ieee.std_logic_1164.all;

library unisim;

use unisim.vcomponents.all;

entity single_stage is

generic (

sh_st: integer:=4);

port (

CLK : in std_logic;

DI : in std_logic;

DO : out std_logic );

end entity single_stage;

architecture recursive of single_stage is

component single_stage

generic (

sh_st: integer);

port (

CLK : in std_logic;

DI : in std_logic;

DO : out std_logic );

end component;

signal tmp : std_logic;

begin

GEN_FD_LAST: if sh_st=1 generate

inst_fd: FD port map (D=>DI, C=>CLK, Q=>DO);

end generate;

GEN_FD_INTERM: if sh_st /= 1 generate

inst_fd: FD port map (D=>DI, C=>CLK, Q=>tmp);

inst_sstage: single_stage

generic map (sh_st => sh_st-1)

port map (DI=>tmp, CLK=>CLK, DO=>DO);

end generate;

end recursive;

```

# **VHDL** Component Configuration

A component configuration explicitly links a component with the appropriate model.

- A model is an entity and architecture pair.

- XST supports component configuration in the declarative part of the architecture.

for instantiation\_list : component\_name use

LibName.entity Name(Architecture Name);

- The statement below indicates that:

- All NAND2 components use the design unit consisting of entity NAND2 and architecture ARCHI.

- The design unit is compiled in the work library.

For all : NAND2 use entity work.NAND2(ARCHI);

- If the configuration clause is missing for a component instantiation:

- XST links the component to the entity with the same name (and same interface).

- XST links the selected architecture to the most recently compiled architecture.

- XST generates a Black Box during synthesis if no entity or architecture is found.

- In command line mode, you may use a dedicated configuration declaration to link component instantiations to design entities and architectures.

- The value of the mandatory Top Module Name (-top) option in the run command is the configuration name instead of the top level entity name.

# VHDL Generics

VHDL generics:

- Are the equivalent of Verilog parameters.

- Help you create scalable design modelizations.

- Allow you to write compact, factorized VHDL code.

- Allow you to parameterize functionality such as:

- Bus sizes

- The amount of certain repetitive elements in the design unit

#### Parameterize Functionality Example

For the same functionality that must be instantiated multiple times, but with different bus sizes, you need describe only one design unit with generics. See *VHDL Generic Parameters Coding Example* below.

#### **Declaring Generics**

You can declare generic parameters in the entity declaration part.

- XST supports all types for generics including:

- integer

- boolean

- string

- real

- std\_logic\_vector

- Declare a generic with a default value.

\_ \_

#### **VHDL Generic Parameters Coding Example**

```

-- VHDL generic parameters example

_ _

-- Download: http://www.xilinx.com/txpatches/pub/documentation/misc/xstug_examples.zip

-- File: VHDL_Language_Support/generics/generics_1.vhd

_ _

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity addern is

generic (

width : integer := 8);

port (

A,B : in std_logic_vector (width-1 downto 0);

Y : out std_logic_vector (width-1 downto 0) );

end addern;

architecture bhv of addern is

begin

Y \leq A + B;

end bhv;

Library IEEE;

use IEEE.std_logic_1164.all;

entity top is

port (

X, Y, Z : in std_logic_vector (12 downto 0);

A, B : in std_logic_vector (4 downto 0);

S :out std_logic_vector (17 downto 0) );

end top;

architecture bhv of top is

component addern

generic (width : integer := 8);

port (

A,B : in std_logic_vector (width-1 downto 0);

Y : out std_logic_vector (width-1 downto 0) );

end component;

for all : addern use entity work.addern(bhv);

signal C1 : std_logic_vector (12 downto 0);

signal C2, C3 : std_logic_vector (17 downto 0);

begin

Ul : addern generic map (width=>13) port map (X,Y,Cl);

C2 <= C1 & A;

C3 <= Z & B;

U2 : addern generic map (width=>18) port map (C2,C3,S);

end bhv;

```

# **Conflicts Among VHDL Generics and Attributes**

Conflicts can arise among VHDL generics and attributes because:

• You can apply VHDL generics and attributes to both *instances* and *components* in the HDL source code.

AND

• You can specify *attributes* in a constraints file.

# **Rules for Conflict Resolution**

XST resolves the conflicts among VHDL generics and attributes as follows:

- Specifications on an *instance* (lower level) take precedence over specifications on a *component* (higher level).

- If a generic and an attribute are applicable to the same instance or the same component, the attribute takes precedence over the generic, regardless of where the generic was specified.

Do not use both mechanisms to define the same constraint. XST flags such occurrences.

- An attribute specified in the XST Constraint File (XCF) takes precedence over attributes or generics specified in the VHDL code.

- Security attributes on the block definition take precedence over any other attribute or generic.

This information is summarized in the following table.

# **Rules for Conflict Resolution Summary**

| Item                                                 | Takes Precedence Over                                      |

|------------------------------------------------------|------------------------------------------------------------|

| Specifications on an instance (lower level)          | Specifications on a component (higher level)               |

| Attribute applied to an instance or component        | Generic applied to the same instance or the same component |

| Attribute specified in the XST Constraint File (XCF) | Attributes or generics specified in the VHDL code          |

| Security attributes on the block definition          | Any other attribute or generic                             |

# **VHDL Combinatorial Circuits**

XST supports the following VHDL combinatorial circuits:

- VHDL Concurrent Signal Assignments

- VHDL Generate Statements

- VHDL Combinatorial Processes

# **VHDL Concurrent Signal Assignments**

Combinatorial logic is described using concurrent signal assignments.

- Concurrent signal assignments are specified in the body of an architecture.

- VHDL supports three types of concurrent signal assignments:

- Simple

- Selected (with-select-when)

- Conditional (when-else)

- You can describe as many concurrent signal assignments as are necessary.

- The order of appearance of the concurrent signal assignments in the architecture is irrelevant.

- All concurrent signal assignments are concurrently active.

- A concurrent signal assignment is re-evaluated when any signal on the right side of the assignment changes value.

- The re-evaluated result is assigned to the signal on the left-hand side.

#### Simple Signal Assignment VHDL Coding Example

$T \le A$  and B;

#### **Concurrent Selection Assignment VHDL Coding Example**

```

-- Concurrent selection assignment in VHDL

_ _

-- Download: http://www.xilinx.com/txpatches/pub/documentation/misc/xstug_examples.zip

-- File: VHDL_Language_Support/combinatorial/concurrent_selected_assignment.vhd

_ _

library ieee;

use ieee.std_logic_1164.all;

entity concurrent_selected_assignment is

generic (

width: integer := 8);

port (

a, b, c, d : in std_logic_vector (width-1 downto 0);

sel : in std_logic_vector (1 downto 0);

T : out std_logic_vector (width-1 downto 0) );

end concurrent_selected_assignment;

architecture bhv of concurrent_selected_assignment is

begin

with sel select

T \leq a when "00",

b when "01",

c when "10",

d when others;

end bhv;

```

\_ \_

#### Concurrent Conditional Assignment (When-Else) VHDL Coding Example

```

-- A concurrent conditional assignment (when-else)

_ _

-- Download: http://www.xilinx.com/txpatches/pub/documentation/misc/xstug_examples.zip

-- File: VHDL_Language_Support/combinatorial/concurrent_conditional_assignment.vhd

_ _

library ieee;

use ieee.std_logic_1164.all;

entity concurrent_conditional_assignment is

generic (

width: integer := 8);

port (

a, b, c, d : in std_logic_vector (width-1 downto 0);

sel : in std_logic_vector (1 downto 0);

T : out std_logic_vector (width-1 downto 0) );

end concurrent_conditional_assignment;

architecture bhv of concurrent_conditional_assignment is

begin

T \le a when sel = "00" else

b when sel = "01" else

c when sel = "10" else

d;

end bhv;

```

# **VHDL Generate Statements**

VHDL generate statements include:

- VHDL For-Generate Statements

- VHDL If-Generate Statements

# **VHDL For-Generate Statements**

VHDL for-generate statements describe repetitive structures.

#### For-Generate Statement VHDL Coding Example

In this coding example, the **for-generate** statement describes the calculation of the result and carry out for each bit position of this 8-bit Adder.

```

-- A for-generate example

_ _

-- Download: http://www.xilinx.com/txpatches/pub/documentation/misc/xstug_examples.zip

-- File: VHDL_Language_Support/combinatorial/for_generate.vhd

_ _

entity for_generate is

port (

A,B : in BIT_VECTOR (0 to 7);

CIN : in BIT;

SUM : out BIT_VECTOR (0 to 7);

COUT : out BIT );

end for_generate;

architecture archi of for_generate is

signal C : BIT_VECTOR (0 to 8);

begin

C(0) \leq CIN;

COUT <= C(8);

LOOP_ADD : for I in 0 to 7 generate

SUM(I) \leq A(I) \text{ xor } B(I) \text{ xor } C(I);

C(I+1) \leq (A(I) \text{ and } B(I)) \text{ or } (A(I) \text{ and } C(I)) \text{ or } (B(I) \text{ and } C(I));

end generate;

end archi;

```

# **VHDL If-Generate Statements**

- An **if-generate** statement activates specific parts of the HDL source code based on a test result.

- The if-generate statement is supported for static (non-dynamic) conditions.

#### **If-Generate Example**

- A generic indicates which device family is being targeted.

- The **if-generate** statement:

- Tests the value of the generic against a specific device family.

- Activates a section of the HDL source code written specifically for that device family.

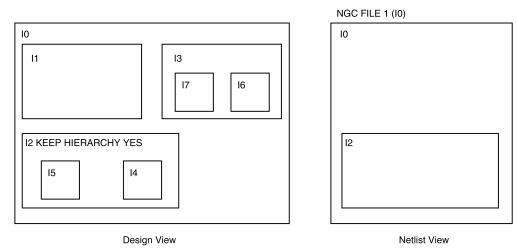

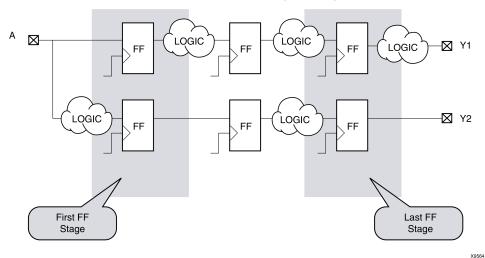

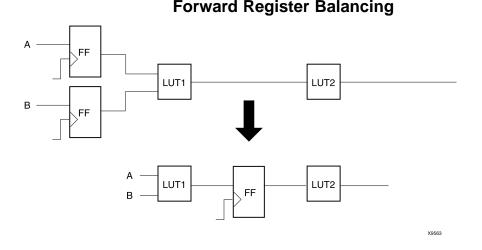

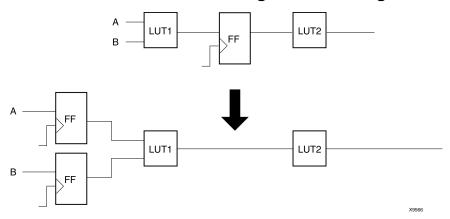

#### For-Generate Nested in an If-Generate Statement VHDL Coding Example