## Xilinx Tool Introduction Getting Started - Schematic Based rev 9/20/20

- 0) Create a directory (folder) for a new design. Open a terminal window and make the new folder the current directory: Use the cd nnnnn command, where nnnnn is the name of the newly created directory.

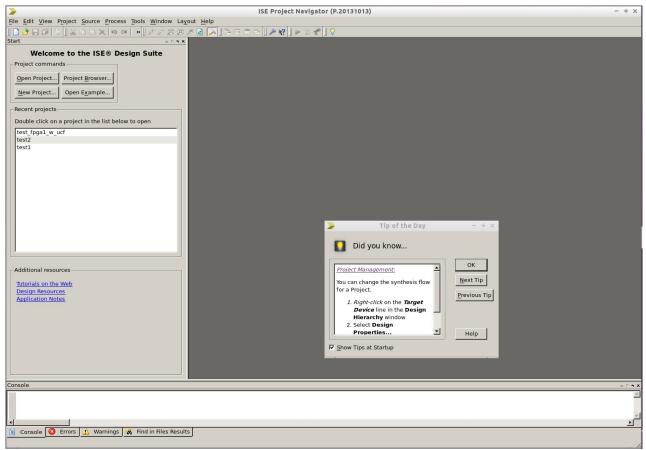

- 1) Start the Xilinx 14 ISE software by entering **ise** in the terminal window and pressing enter (note the command is lower case).

ISE may start up with a prior design loaded. If so, click **File** on the tool bar and select **close**. You can also click OK in the Tip-Of-The-Day window.

2) In the upper left four "buttons" will be displayed.

Create a new project by clicking on the New Project. button

a) A *New Project Wizard* pop-up window will open. The path to a prior project may be shown. Before entering the name of a new project, select the directory (folder) where the new project will be created. Click the little box with dots (...) to the right of the **Location** field and navigate to the desired directory (folder) where you wish to place your design.

|                                                                   | New Project Wizard                           | - + >  |

|-------------------------------------------------------------------|----------------------------------------------|--------|

| Create New Project<br>Specify project loo                         |                                              |        |

| Enter a name, locat                                               | ions, and comment for the project            |        |

| N <u>a</u> me:                                                    | demo1circuit                                 |        |

| Location:                                                         | /home/aamola/ee433/fall15/demo1/demo1circuit |        |

| Working Directory:                                                | /home/aamola/ee433/fall15/demo1/demo1circuit |        |

| <u>D</u> escription:                                              |                                              |        |

| Select the type of to<br><u>T</u> op-level source ty<br>Schematic | op-level source for the project              |        |

| More Info                                                         | Next >                                       | Cancel |

|                                                                   | <u></u> ext >                                | curren |

- b) Type in a project name (it will show up in the Location field also as you type)

- c) Select Schematic as the type of top-level source for the project.

- d) Click Next

- e) The *Project Settings* screen should appear. Set it up as follows:

| Evaluation Dev Board   | None specified                                     |

|------------------------|----------------------------------------------------|

| Product Category       | General Purpose                                    |

| Family                 | Spartan6                                           |

| Device                 | XC6SLX16                                           |

| Package                | FTG256                                             |

| Speed                  | -5                                                 |

| Top-level Source Type  | Schematic (this field may be grayed out. Thats ok) |

| Synthesis Tool         | XST (VHDL/Verilog)                                 |

| Simulator              | ISim (VHDL/Verilog)                                |

| Preferred Language     | VHDL                                               |

| Property specification | Store all values                                   |

- f) Click Next

- g) The *Project Summary* screen should appear. Look over the information. If something is not as you desire then use the **Back** button to go back and make a correction. Otherwise click **Finish**.

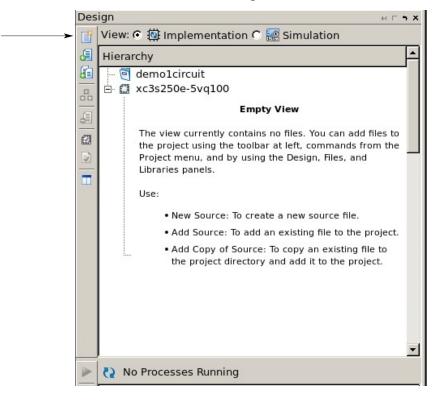

h) In the upper left of the screen is a box with the words Hierarchy at the top. Just left of that are a row of iconic buttons. The top icon is New Source. Click on it.

i) The *Create New Source* wizard window should appear. Click on **Schematic** and then type in a file name. I suggest using **top\_sch\_projname** where projname is a name to associate with your project (in the example shown I just use top\_schematic but you can do better). Since designs can be created hierarchically this naming convention will make clear that this is the highest level of your design and is a schematic type design block. Click **Next**. The *New Source Wizard Summary* will be displayed. Click **Finish**.

| > New Source                                                                                                                                                                                                                                                                         | Wizard - + ×                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Select Source Type<br>Select source type, file name and its lo                                                                                                                                                                                                                       | cation.                                                                                           |

| <ul> <li>IP (CORE Generator &amp; Architecture Wiza</li> <li>Schematic</li> <li>User Document</li> <li>Verilog Module</li> <li>Verilog Test Fixture</li> <li>VHDL Module</li> <li>VHDL Library</li> <li>VHDL Package</li> <li>VHDL Test Bench</li> <li>Embedded Processor</li> </ul> | <u>F</u> ile name:<br>top_schematic<br>Lo <u>c</u> ation:<br>hola/ee433/fall15/demo1/demo1circuit |

|                                                                                                                                                                                                                                                                                      | ✓ Add to project                                                                                  |

| More Info                                                                                                                                                                                                                                                                            | <u>N</u> ext > Cancel                                                                             |

You may be told that the directory xxx/nnnnn (xxx represents a path string) does not exist, would you like to create it? Answer yes.

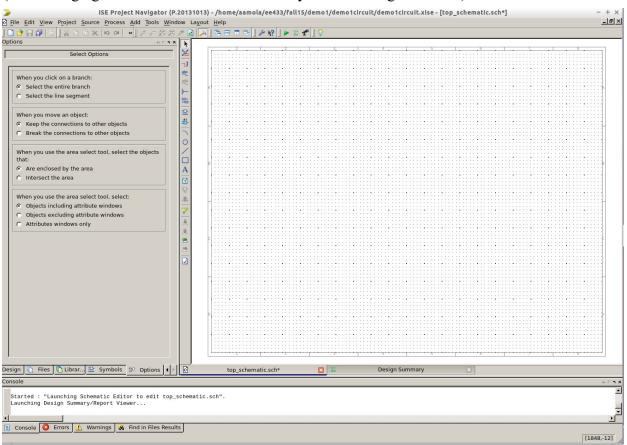

A blank schematic sheet should appear in the right 2/3 of the ISE window. And on the left you should see a subwindow with several tabs at the bottom. Tabs include Design, Files, Library, Symbols, Options.

| e Edit View Project Source Process Add Tools<br>경 🕞 🕼 😓 🖌 🗅 🔿 🗶 🗠 여 🖉 » 🕽 🍠 🔎 |              |                   | ve 🎤 II 🔿 |                |      |

|-------------------------------------------------------------------------------|--------------|-------------------|-----------|----------------|------|

|                                                                               |              |                   | ₩ 🛪 🔟 V   |                | <br> |

| Select Options                                                                | - 2          |                   |           | · _ · _ ·      |      |

| Select Options                                                                | - 1          |                   |           |                |      |

|                                                                               |              |                   |           |                |      |

| When you click on a branch:                                                   | abc<br>a(0)  |                   |           |                |      |

| <ul> <li>Select the entire branch</li> </ul>                                  |              |                   |           |                |      |

| Select the line segment                                                       |              |                   |           |                |      |

|                                                                               | 90           |                   |           |                |      |

| When you move an object:                                                      | ₽.           |                   |           |                |      |

| <ul> <li>Keep the connections to other objects</li> </ul>                     | 4            | -                 |           |                |      |

| Break the connections to other objects                                        | 7            |                   |           |                |      |

|                                                                               | 0            |                   |           |                |      |

| When you use the area select tool, select the objects                         | /            |                   |           |                |      |

| :hat:                                                                         |              |                   |           |                |      |

| <ul> <li>Are enclosed by the area</li> </ul>                                  | A            |                   |           |                |      |

| Intersect the area                                                            |              |                   |           |                |      |

|                                                                               |              |                   |           |                |      |

| When you use the area select tool, select:                                    |              |                   |           |                |      |

| <ul> <li>Objects including attribute windows</li> </ul>                       | 1111         | -                 |           |                |      |

| Objects excluding attribute windows                                           | ~            |                   |           |                |      |

| Attributes windows only                                                       | *            |                   |           |                |      |

|                                                                               | <u>&amp;</u> |                   |           |                |      |

|                                                                               | 95           |                   |           |                |      |

|                                                                               | 唐            |                   |           |                |      |

|                                                                               |              |                   |           |                |      |

|                                                                               |              |                   |           |                |      |

|                                                                               |              | -                 |           |                |      |

|                                                                               |              |                   |           |                |      |

|                                                                               |              |                   |           |                |      |

|                                                                               |              |                   |           |                |      |

|                                                                               |              |                   |           |                |      |

|                                                                               |              |                   |           |                |      |

|                                                                               |              |                   |           |                |      |

|                                                                               |              |                   |           |                |      |

|                                                                               |              |                   |           |                |      |

|                                                                               |              |                   |           |                |      |

| n 🚺 Files 🚺 Librar 🔛 Symbols 🜮 Options                                        | ۰ ۲          | top_schematic.sch | 2         | Design Summary |      |

| le                                                                            |              |                   |           |                | н    |

| arted : "Launching Schematic Editor to edit                                   | top schemati | c.sch".           |           |                |      |

| unching Design Summary/Report Viewer                                          |              |                   |           |                |      |

| anoning beargit cammar jritepore rizener i ir                                 |              |                   |           |                |      |

| anoning boorgi cummar ji nopor e fizikor fifi                                 |              |                   |           |                |      |

a) Right click on the schematic in the right window and then click Object Properties at the bottom of the pop-up menu. A sheet size of 22x17 (C size) will be shown. Click on C=22x17 below size which should open a list of sheet sizes. For your first simple design click on A=11x8.5 and then click OK.

Note 1: For designs larger than the initial test design you likely will wish to use a B or C size sheet.

## (after changing sheet size to A the screen likely will show a grid of dots)

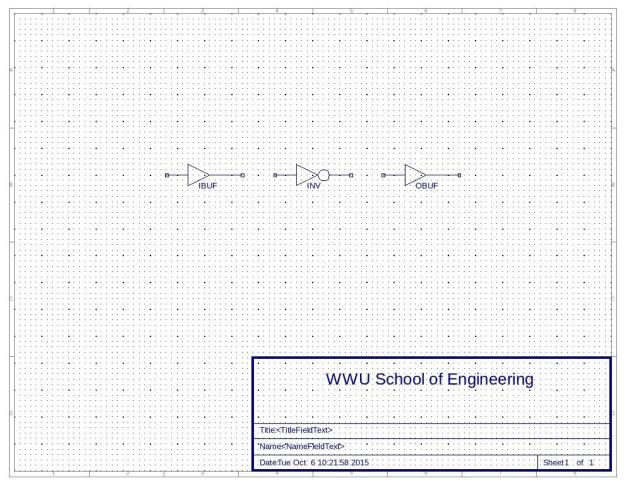

- 4) The goal now is to create a simple circuit. The circuit will be a signal coming in to an invertor and then going out again. Three circuit components (ibuf, inv, obuf) and two connectivity symbols for specifying connections to the outside world will be required.

- a) Click on the Symbols tab at the bottom of the left subwindow. Two smaller windows should open with the top labeled *Categories* and the lower *Symbols*.

- b) Click on category General and symbol Title. Move the cursor right and a title block will move over the schematic sheet. Move it towards the lower right corner of the sheet and click. Hit the Escape key to unconnect the cursor from the symbol. Then grab the top edge of the title block by positioning the cursor over it and holding down the left mouse button. Move the symbol tight into the lower right corner of the sheet and release. XILINX will be displayed in the title block but that can be edited. More on that later.

(here is the finished circuit)

| <br> |     |

|------|-----|

|      | 1   |

|      | 1 2 |

|      | 1/  |

|      |     |

Place circuit components on the schematic.

- c) In the *Categories* window click on **I/O** (scroll if needed). Then find **ibuf** (input buffer) in the *Symbols* window below and click it. Move your cursor to a location toward the left of the schematic sheet and centered vertically above the title block. Click once.

- d) Repeat for **obuf** placing it horizontally aligned with ibuf but to the right on the sheet.

- e) In the *Categories* window select **Logic** and in the *Symbols* window find **inv** and place between ibuf and obuf.

Next the inverter needs to be wired to the input and output buffers.

d) Along the left edge of the schematic window is a Tool bar. The third icon down is the Add Wire tool. Select that.. On the schematic, single left click at the point to start a wire and single left click where you wish it to end.

Next an I/O marker must be added to the ibuf input and obuf output.

e) On the tool bar at schematic left, select Add I/O Marker (7<sup>th</sup> icon down). Left click on the end of the wire going into the ibuf. Then left click on the end of the wire coming out of the obuf. The I/O marker symbols will have an auto generated name in them.

Attributes of the I/O markers need to be changed to identify the physical pin on the FPGA that they are associated with and the marker name can be changed to reflect the signal name. Pin numbers start with capital letter such as H14 etc.

f) Right click on the I/O marker and a pop-up menu will appear. Click on Object Properties. An Object Properties window will open. On the left under Category click on Nets. Towards the right of the window click on the New button. A New Attribute window will open with the default attribute name of LOC. For Attribute Name type in a pin number (has to start with a capital letter). Click OK.

Default net names start with XLXN which is cryptic. Change the value of the Name attribute to reflect the signal on that net. For example, in1, out1, or sw0, led0, etc (don't use spaces in net names). Then click OK.

g) Repeat for other I/O markers. For example, the output might be for LED #0.

(See handout, available on the class web page, defining FPGA pinout & function).

| ð      | New At       | tribute      | - + ×    |

|--------|--------------|--------------|----------|

| Attrib | ute name     |              |          |

| LOC    |              |              | -        |

| _      | ute value    |              | P        |

| P2     |              |              |          |

|        | ute value ty | pe           |          |

| Strin  | 9            |              | <u> </u> |

| ☐ Re   | member this  | attribute na | ame      |

|        | ОК           | Cancel       | Help     |

|        |              |              |          |

- 5) When all parts are added and wired up you can do what is called Design Rule Check (DRC) of the schematic. This check does not tell you that the circuit will work, only that signals are connected to component inputs, etc. Messages from the DRC check are displayed in the transcript window at the bottom of the screen. DRC knows nothing about what your circuit is suppose to do.

- a) From the tool bar at the left of the schematic click on the check mark symbol, 6<sup>th</sup> up from the bottom.

- 6) The time has come to synthesize the FPGA configuration information from the schematic you have entered.

- a) First, set up display of useful information. Under the schematic click the tab labeled **Design Summary**. Then from the lower left tabs click on **Design**.

- b) Then on the horizontal tool bar at the top is a green arrow symbol., the **Implement Top Module button**. Left click the green arrow.

It may ask if you wish to save changes. If you don't save it will use the design as it was prior to your last edit. The Implement step will take some time. Be patient. There can be several seconds delay from when you click and when new info appears on the screen while program code is downloaded from the server and run. There are several different programs that run. Information will scroll by in the transcript window if it is open and the Design Summary window will update.

Watch the sequence of results as synthesis, place, and route occur.

c) Next, in the lower left window double click **Generate Programming File** to generate the bit map file that will be downloaded to configure the FPGA

| File Edit View Project Source Process Tools Window           |       | e/aamola/ee433/fall15/demo1/der<br>out Help                    | no1circuit/demo1ci                             | rcuit.xise  | e - [Desig  | In Summa    | ary (Progra  | amming F             | ile Ge | enerated)]     |                     | - +<br>    |

|--------------------------------------------------------------|-------|----------------------------------------------------------------|------------------------------------------------|-------------|-------------|-------------|--------------|----------------------|--------|----------------|---------------------|------------|

| 원였으느, ····································                   |       |                                                                | *                                              |             |             |             |              |                      |        |                |                     |            |

| Design ↔ K                                                   | 0     | 🖻 Design Overview                                              |                                                | top         | schemat     | ic Project  | t Status (10 | 0/06/2015            | - 13:  | 11:10)         |                     |            |

| 👔 View: 🕫 🔯 Implementation Ҁ 🔝 Simulation                    | e     | Summary     IOB Properties                                     | Project File:                                  | demo1cir    |             |             | arser Erro   |                      |        | No Errors      |                     |            |

| Hierarchy                                                    | ē     | - 🖹 Module Level Utilization                                   | Module Name:                                   | top_sche    | matic       | Ir          | mplementa    | tion State           |        | Programmir     | g File Generate     | d          |

| i emolcircuit<br>□ : : xc3s250e-5vq100                       | 5     | D clash Denset                                                 | Target Device:                                 | xc3s250e    |             |             | • Errors     |                      |        | No Errors      | 5                   |            |

|                                                              | -     |                                                                | Product Version:                               | ISE 14.7    |             |             | • Warnii     |                      |        | 2 Warnings     | (2 new)             |            |

|                                                              | 36    | Static Timing                                                  | Design Goal:                                   | Balanced    | 1           |             |              | g Results            | :      |                | completely Rou      | ted        |

|                                                              | X     | - Crois and Warnings                                           | Design Strategy:                               | Xilinx De   | fault (unlo | cked)       |              | Constrai             |        |                |                     | _          |

|                                                              | -     | Synthesis Messages                                             | Environment:                                   | System S    |             |             |              | '<br>iming Sco       |        |                |                     |            |

|                                                              |       | <ul> <li>Translation Messages</li> <li>Map Messages</li> </ul> |                                                |             |             |             |              |                      |        |                |                     |            |

|                                                              |       | - 🖹 Place and Route Messages                                   |                                                |             |             |             | 2            |                      |        |                |                     |            |

|                                                              |       | 🚽 📄 Timing Messages                                            |                                                |             | Devie       | ce Utilizat | tion Summ    |                      |        |                |                     | Ð          |

|                                                              |       | 🔤 All Implementation Messa                                     | Logic Utilization                              |             |             |             |              | Available            |        | tilization     | Note(s)             |            |

|                                                              |       | Detailed Reports                                               | Number of Slices of                            |             | -           | -           | 0            |                      | 0      | 0%             |                     |            |

|                                                              |       | - 📄 Translation Report                                         | Number of Slices of                            | -           | unrelated I | logic       | 0            |                      | 0      | 0%             |                     |            |

|                                                              |       | Map Report                                                     | Number of bonded IC                            |             |             |             | 2            |                      | 66     | 3%             |                     |            |

|                                                              |       | - 📄 Place and Route Report<br>- 📄 Post-PAR Static Timing Re    | Average Fanout of No                           | n-Clock Ne  | ets         |             | 1.00         |                      |        |                |                     |            |

|                                                              |       | 🗋 Power Report                                                 |                                                |             |             |             |              |                      |        |                |                     |            |

| No Processes Running                                         |       | Bitgen Report Secondary Reports                                |                                                |             | Pe          | rformance   | e Summar     | /                    |        |                |                     | [-]        |

| Processes: top_schematic                                     |       | WebTalk Report                                                 | Final Timing Score                             |             | 0 (Setup: 0 | , Hold: 0)  |              | Pino                 | ut Da  | ta: Pi         | nout Report         |            |

| Design Summary/Reports                                       |       | 🔤 WebTalk Log File                                             | Routing Results:                               | 1           | All Signals | Completel   | y Routed     | Cloc                 | k Dat  | a: <u>C</u>    | ock Report          |            |

| B S User Constraints                                         |       | Design Properties                                              | Timing Constraints                             | :           |             |             |              |                      |        |                |                     |            |

| Synthesize - XST                                             |       | Enable Message Filtering                                       |                                                |             |             |             |              |                      |        |                |                     |            |

| Implement Design     Generate Programming File               |       | Optional Design Summary Contents                               |                                                |             |             |             | _            |                      |        |                |                     |            |

| 🖶 🛞 Configure Target Device                                  |       | Show Failing Constraints                                       |                                                |             | 1           | Detailed    |              |                      |        |                |                     | Ð          |

| Analyze Design Using ChipScope                               |       | Show Warnings Show Errors                                      | Report Name                                    |             | Status      | Generate    |              | Error                |        | arnings        | Infos               |            |

|                                                              |       |                                                                | Synthesis Report                               |             | Current     |             | 13:09:04 20  |                      |        | Warning (1 nev | _                   |            |

|                                                              |       |                                                                | Translation Report                             |             | Current     |             | 13:09:12 20  |                      | 0      |                | 0                   |            |

|                                                              |       |                                                                | Map Report                                     |             | Current     |             | 13:09:21 20  |                      |        | Warning (1 nev |                     |            |

|                                                              |       |                                                                | Place and Route Repo                           | ort         | Current     | Tue Oct 6   | 13:09:31 20  | 15 0                 | 0      |                | <u>1 Info (1 ne</u> | <u>aw)</u> |

|                                                              |       |                                                                | Power Report                                   |             |             |             |              |                      |        |                |                     |            |

| 🔹 Design 👔 Files 🚺 Librar 🔛 Symbols 🜮 Op 📢                   | 16    | top_schematic.sch 🛛 🗏 Des                                      | Post-PAR Static Timir<br>sign Summary (Progran |             |             |             |              | 15  0<br>f_title.sym | 0      |                | 6 Infos (6 r        | new)       |

|                                                              | 11 -  |                                                                | sign Summary (Flogram                          | inning rife | Generated   |             | cobàTo       | r_coc.sym            | 6      |                |                     |            |

| onsole<br>Command Line: bitgen -intstyle ise -f top_schemati | с. ut | t top schematic ocd                                            |                                                |             |             |             |              |                      |        |                |                     | HE         |

|                                                              |       |                                                                |                                                |             |             |             |              |                      |        |                |                     |            |

|                                                              | esst  | титту                                                          |                                                |             |             |             |              |                      |        |                |                     |            |

| Process "Generate Programming File" completed succ           |       |                                                                |                                                |             |             |             |              |                      |        |                |                     |            |

| Process "Generate Programming File" completed succ           |       |                                                                |                                                |             |             |             |              |                      |        |                |                     | <u> </u>   |

| Process "Generate Programming File" completed succ           | ts    |                                                                |                                                |             |             |             |              |                      |        |                |                     | <u>,</u>   |

7) Downloading the design to the FPGA

At this point make sure that the programming cable is connected between computer and FPGA board and then apply power to the FPGA board.

Double click **Configure Target Device** to start the iMPACT program. A Project Navigator window may open warning that no iMPACT project file exists. Click **OK**.

The initial screen may look like this:

|                                                  | ISE IMPACT (P.20131013)          | - + ×          |

|--------------------------------------------------|----------------------------------|----------------|

| File Edit View Operations Output Deb             | bu <u>q W</u> indow <u>H</u> elp |                |

| ] 🗋 ờ ] 🍫 - ] 着 🗉 ] 🎤 🗞                          |                                  |                |

| iMPACT Flows ↔ ┌ ┾                               |                                  |                |

| Boundary Scan                                    |                                  |                |

| - 📄 SystemACE<br>- 📄 Create PROM File (PROM File |                                  |                |

| WebTalk Data                                     |                                  |                |

|                                                  |                                  |                |

|                                                  |                                  |                |

|                                                  |                                  |                |

| iMPACT Processes ↔ ┌ ┾                           |                                  |                |

|                                                  |                                  |                |

|                                                  |                                  |                |

|                                                  |                                  |                |

|                                                  |                                  |                |

|                                                  |                                  |                |

|                                                  |                                  |                |

|                                                  |                                  |                |

| Console                                          |                                  | н Г <b>ч х</b> |

|                                                  |                                  | <u> </u>       |

|                                                  |                                  |                |

| Errors 🔬 Warnings                                |                                  |                |

|                                                  |                                  |                |

|                                                  |                                  |                |

Double click on Boundary Scan. The larger area to the right should turn white with a message "Right click to select device ....". Right click and in the pop-up box that appears select Cable Setup. The cable setup box looks like this:

| Gable Communication Setup − + ×                     |  |  |  |  |

|-----------------------------------------------------|--|--|--|--|

| Communication Mode                                  |  |  |  |  |

| C Parallel Cable III C Platform Cable USB/II        |  |  |  |  |

| C Parallel Cable IV © Digilent USB JTAG Cable       |  |  |  |  |

| C HW Server                                         |  |  |  |  |

| Advanced USB Cable Setup                            |  |  |  |  |

| Port: TCK Speed/Baud Rate:                          |  |  |  |  |

| JtagHs2/210249A0D649 💌 Default Speed 💌              |  |  |  |  |

| Cable Location                                      |  |  |  |  |

| C Remote Host Name:                                 |  |  |  |  |

| Cable Plug-in                                       |  |  |  |  |

| Copen Cable Plug-in. Select or enter a Plug-in fron |  |  |  |  |

| atformusb PORT=USB21 FREQUENCY=6000000              |  |  |  |  |

| OK Cancel Help                                      |  |  |  |  |

If not already selected, select Digilent USB JTAG Cable. Click OK.

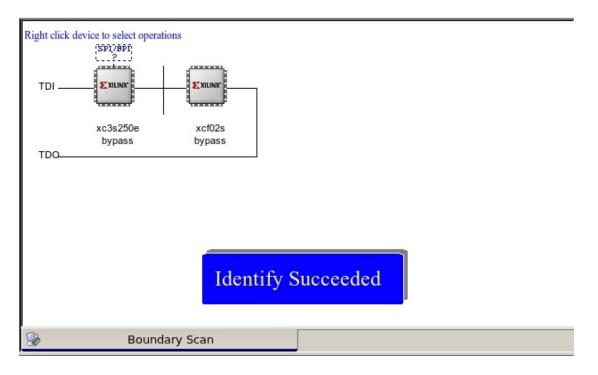

Again right click on the large white window to the right and select Initialize Chain. The right window should look something like this:

| A pop box will ask this: | Auto Assign Configuration Files Query Dialog − + ×         |

|--------------------------|------------------------------------------------------------|

|                          | Do you want to continue and assign configuration files(s)? |

|                          | <u>Y</u> es <u>N</u> o                                     |

**Click Yes**. Configuration filenames have a .bit extension. Navigate if needed to the correct directory where your .bit file is located.

|                                      | Assign New Configuration File                                       |    | - + ×                                  |

|--------------------------------------|---------------------------------------------------------------------|----|----------------------------------------|

| Look in:                             |                                                                     | 30 |                                        |

| File <u>n</u> ame:<br>Files of type: | fpga2_test1.bit<br>All Design Files (*.bit *.rbt *.nky *.isc *.bsd) |    | Open<br>Cancel<br>Bypass<br>Cancel All |

|                                      |                                                                     |    |                                        |

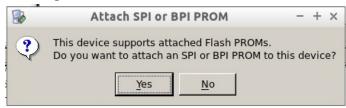

Because there is a second part on the FPGA board a window like this may appear:

Click No. (you don't want to down load to the PROM memory chip)

Even though you said No to attaching the SPI memory part a window like this may open as if to allow selection of a data file to be downloaded to memory. **Click Bypass**:

| Assign New Configuration File                                      | - + ×                                  |

|--------------------------------------------------------------------|----------------------------------------|

| Look in: /home/aamola/ee433/fall16/fpga2_test1_250<br>Compu aamola |                                        |

| Files of type: All Design Files (*.mcs *.isc *.bsd)                | Open<br>Cancel<br>Bypass<br>Cancel All |

The next window is titled Device Programming Properties. It may state that there are no applicable properties for this device. Just click **OK**.

| Device Programming Proper                                                                          | ties - Device 1 Programming Properties                                                                              | - + × |

|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------|

| Device Programming Proper  Category  Boundary-Scan Device 1 (FPGA xc3s250e) Device 2 (PROM xcf02s) | ties - Device 1 Programming Properties  Property Name Verify FPGA Device Specific Programming Properties Pulse PROG | Value |

|                                                                                                    | OK Cancel <u>A</u> pply                                                                                             | Help  |

Believe it or not you are now ready to download the .bit file to the FPGA. In the lower left window double click Program. Or right click on the FPGA in the right window.

Before exiting iMPACT I recommend that you do a cable disconnect under *Output* on the tool bar (Disconnect All Cables).