# Classical State Machine Design

## The Basic Memory Cell

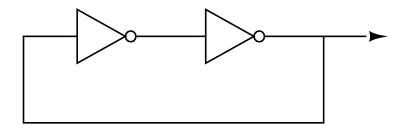

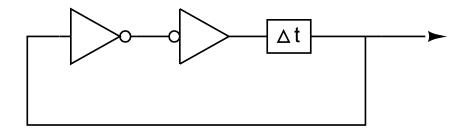

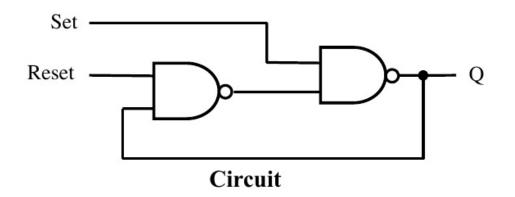

## Consider this circuit:

### The Basic Memory Cell

#### Consider this circuit:

What is the output?

logic high?

logic low?

or something else?

Is this circuit drawn in the best way?

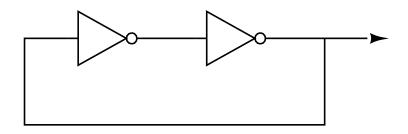

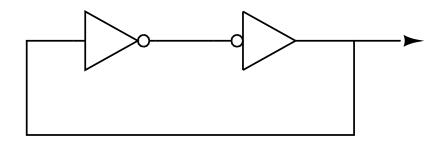

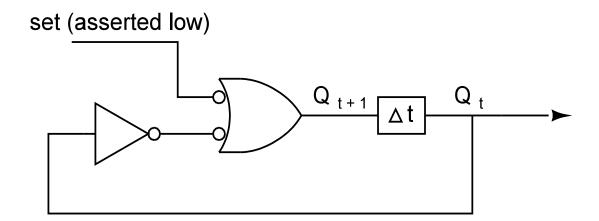

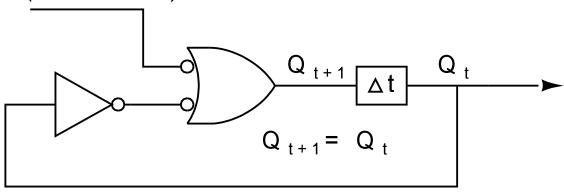

### A better circuit diagram:

Recall that it takes time for signals to propagate through a component

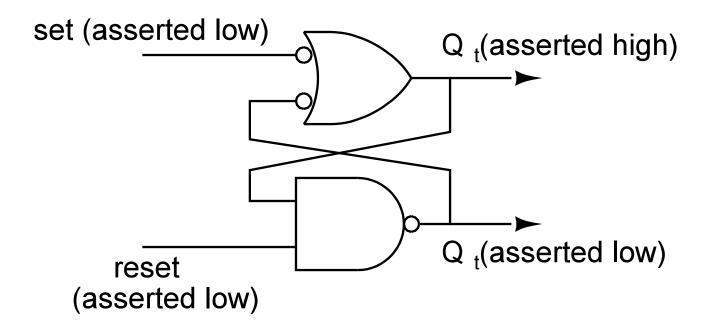

### set (asserted low)

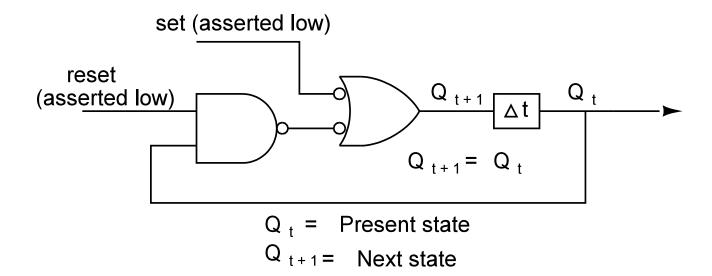

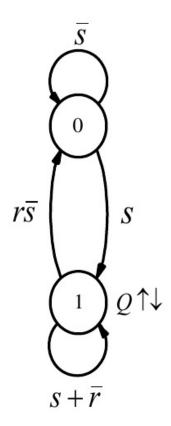

$Q_t$  = Present state

$Q_{t+1} = Next state$

#### Set-dominant Basic Cell

# NAND-Centered (Set Dominant) Basic Cell

- Inputs are active low (when they are asserted);

- Operation table indicates assertion, not voltage, levels.

| S | R | Action | $Q_{N+1}$ |

|---|---|--------|-----------|

| 0 | 0 | hold   | QN        |

| 0 | 1 | reset  | 0         |

| 1 | 0 | set    | 1         |

| 1 | 1 | set    | 1         |

**Operation Table**

|                             | Inputs |        |  |

|-----------------------------|--------|--------|--|

| $Q_{n} \rightarrow Q_{n+1}$ | S      | R      |  |

| $0 \rightarrow 0$           | 0      | $\phi$ |  |

| $0 \rightarrow 1$           | 1      | $\phi$ |  |

| $1 \rightarrow 0$           | 0      | 1      |  |

| $1 \rightarrow 1$           | 1      | $\phi$ |  |

|                             | $\phi$ | 0      |  |

**Excitation Table**

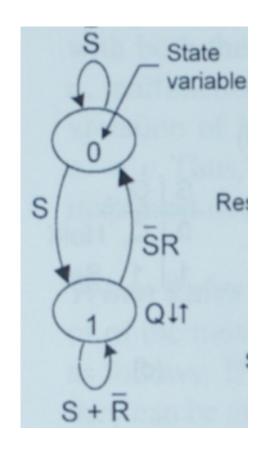

State Diagram

| S | R | Action | Q <sub>N+1</sub> |

|---|---|--------|------------------|

| 0 | 0 | hold   | QN               |

| 0 | 1 | reset  | 0                |

| 1 | 0 | set    | 1                |

| 1 | 1 | set    | 1                |

|                           | Inputs |        |

|---------------------------|--------|--------|

| $Q_n \rightarrow Q_{n+1}$ | S      | R      |

| $0 \rightarrow 0$         | 0      | $\phi$ |

| $0 \rightarrow 1$         | 1      | $\phi$ |

| $1 \rightarrow 0$         | 0      | 1      |

| $1 \rightarrow 1$         | 1      | $\phi$ |

|                           | $\phi$ | 0      |

# **Operation Table**

**Excitation Table**

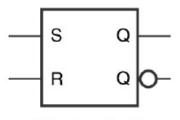

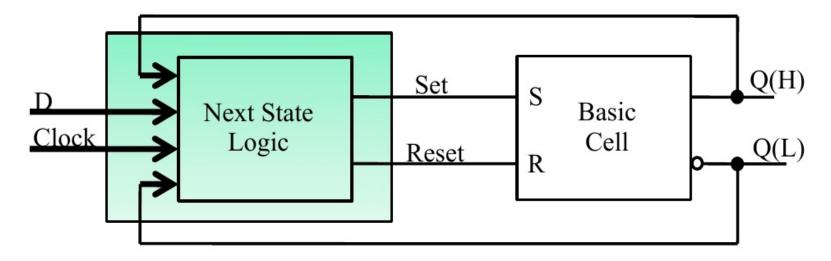

## **Combined Form of the Basic Cell**

| Inputs |               |

|--------|---------------|

| S      | R             |

| 0      | φ             |

| 1      | $\phi$        |

| 0      | 1             |

| 1<br>ø | $_{0}^{\phi}$ |

|        | 0<br>1<br>0   |

**Excitation Table NAND-centered**

|                             | Inp    | uts    |

|-----------------------------|--------|--------|

| $Q_{n} \rightarrow Q_{n+1}$ | S      | R      |

| $0 \rightarrow 0$           | 0      | $\phi$ |

| $0 \rightarrow 1$           | 1      | 0      |

| $1 \rightarrow 0$           | 0      | 1      |

| $1 \rightarrow 1$           | $\phi$ | 0      |

|                             |        |        |

**Excitation Table Combined Form**

|                             | Inputs        |        |

|-----------------------------|---------------|--------|

| $Q_{n} \rightarrow Q_{n+1}$ | S             | R      |

| $0 \rightarrow 0$           | 0<br>ø        | φ<br>1 |

| $0 \rightarrow 1$           | 1             | 0      |

| $1 \rightarrow 0$           | $\phi$        | 1      |

| $1 \rightarrow 1$           | $\phi$ $\phi$ | 0      |

|                             | l             |        |

**Excitation Table NOR-centered**

**Basic Cell**

#### Set dominant basic cell

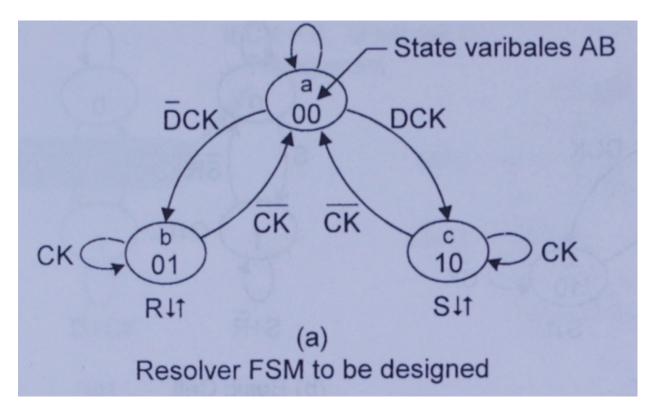

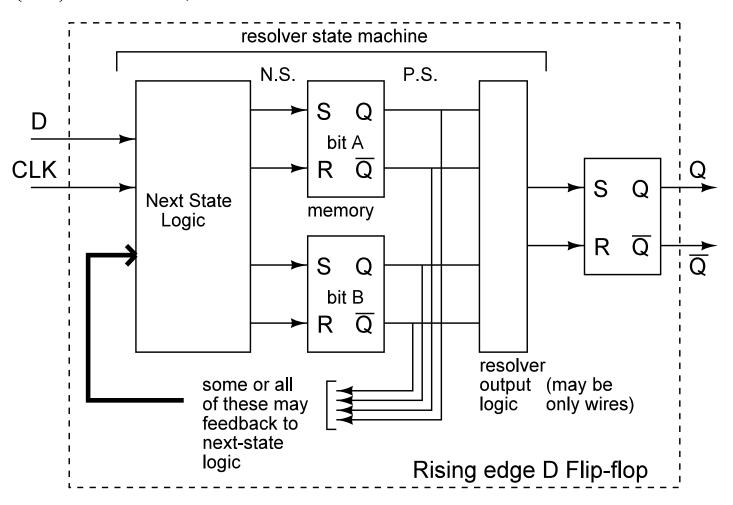

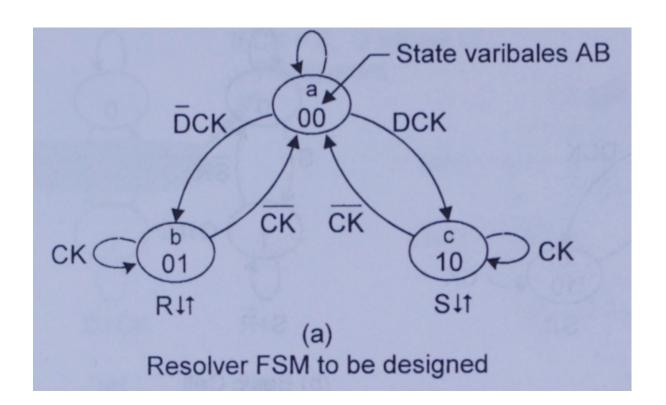

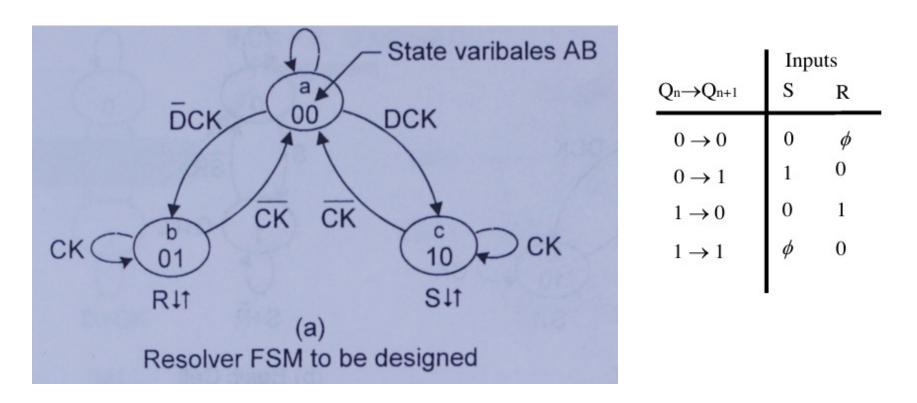

Note that the resolver state diagram has three states and thus two state bits are required. Each state bit will be implemented with a Set-Reset (SR) basic cell, sometimes called an SR-Latch.

|                           | Inp    | Inputs |  |

|---------------------------|--------|--------|--|

| $Q_n \rightarrow Q_{n+1}$ | S      | R      |  |

| $0 \rightarrow 0$         | 0      | $\phi$ |  |

| $0 \rightarrow 1$         | 1      | 0      |  |

| $1 \rightarrow 0$         | 0      | 1      |  |

| $1 \rightarrow 1$         | $\phi$ | 0      |  |

|                           | I      |        |  |

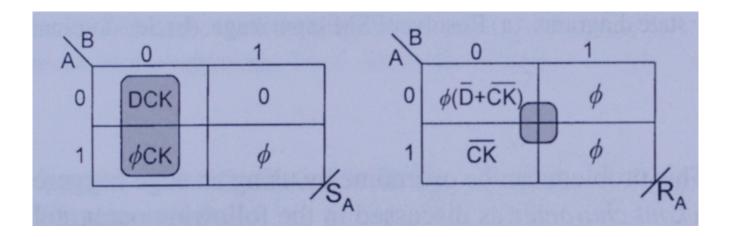

EV-Kmap to document and reduce the needed Next State logic, bit A

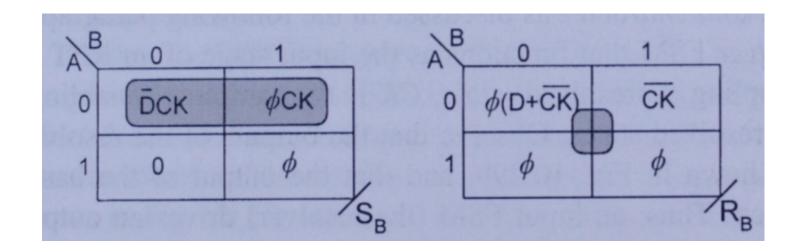

EV-Kmap to document and reduce the needed Next State logic, bit B

blank page