```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity adder_typel is

port (j1, j2, k1, k2, Cin : in std_logic;

Cout, sum : out std_logic);

end adder typel;

architecture adder1 of adder_type1 is

begin

end adder1;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity adder_type2 is

(more statements go here)

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

entity lab4_solution_top is

Port ( A0 : in STD_LOGIC;

Al : in STD LOGIC;

A2 : in STD_LOGIC;

A3 : in STD_LOGIC;

BO : in STD LOGIC;

B1 : in STD LOGIC;

B2 : in STD LOGIC;

B3 : in STD_LOGIC;

Led: out STD_LOGIC_VECTOR (7 downto 0));

end lab4_solution_top;

architecture Behavioral of lab4_solution_top is

component adder_type1

port (j1, j2, k1, k2, Cin :in std_logic;

Cout, sum : out std_logic);

end component;

component adder_type2

port (j1, j2, k, Cin :in std_logic;

Cout, sum : out std_logic);

end component;

signal .... : std_logic;

begin

add1 : adder_type1 port map(A0,B1,A1,B0,'0',c1,Led(1));

end Behavioral;

```

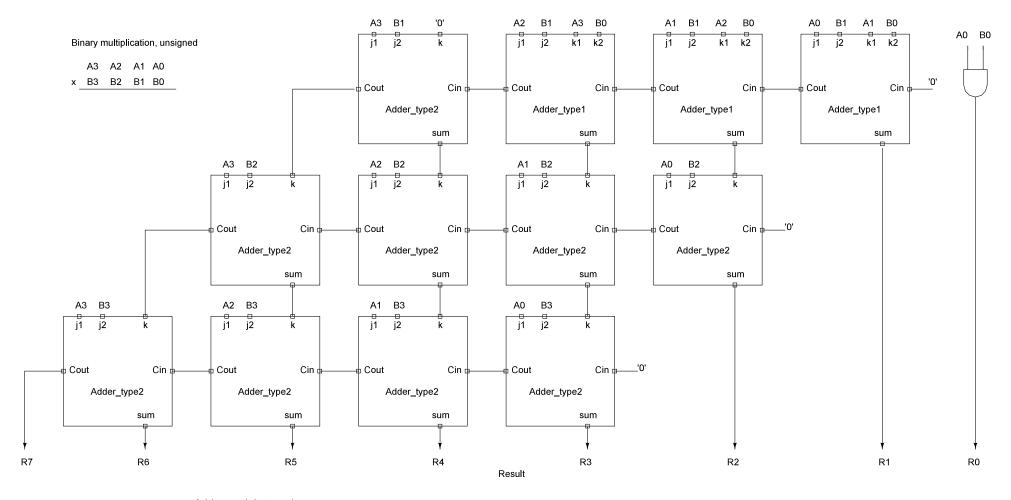

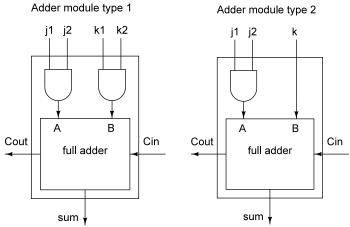

The VHDL shell for lab 4. Note that two components are defined (adder\_type1 and adder\_type2) in the same file as the multiplier, i.e. lab4\_solution. The component statements in the architecture of the multiplier description are needed as shown. The component descriptions could be done in a separate file or two separate files if desired. Because they are quite short, including them with the main description is good.

Note that the actual circuit descriptions of the adder circuits is left to the reader of this note to figure out. Refer to the preceding page and the block diagrams

In the lab4\_solution\_top architecture one copy of an adder is shown. Follow the block diagram to define the rest of the adders and their interconnection. Use a constraints file to make setting up the input/output ports easy..

A few other things to note:

- 1) The library IEEE statements are needed prior to each instance of an entity, as shown.

- 2) The order of the signal names listed in the port map of the instantiated adder\_type1 (named add1) is the order that signals are defined in the adder\_type1 entity, specifically j1, j2, k1, k2, Cin, Cout, sum. That means that incoming signal A0 connects to j1 in the adder, B1 to j2, etc.

- 3) Each signal that goes between blocks in the block diagram, such as Cout going to Cin needs to have a unique name and be defined in the architecture prior to the begin statement

- A) Names defined in the entity of a component, such as adder\_type1 or adder\_type2, or within their architecture, are local to the component and not visible from the lab4\_solution\_top architecture.