# A First Look at Microcontroller Configuration

Kinetis L-Series KL25Z128VLK4

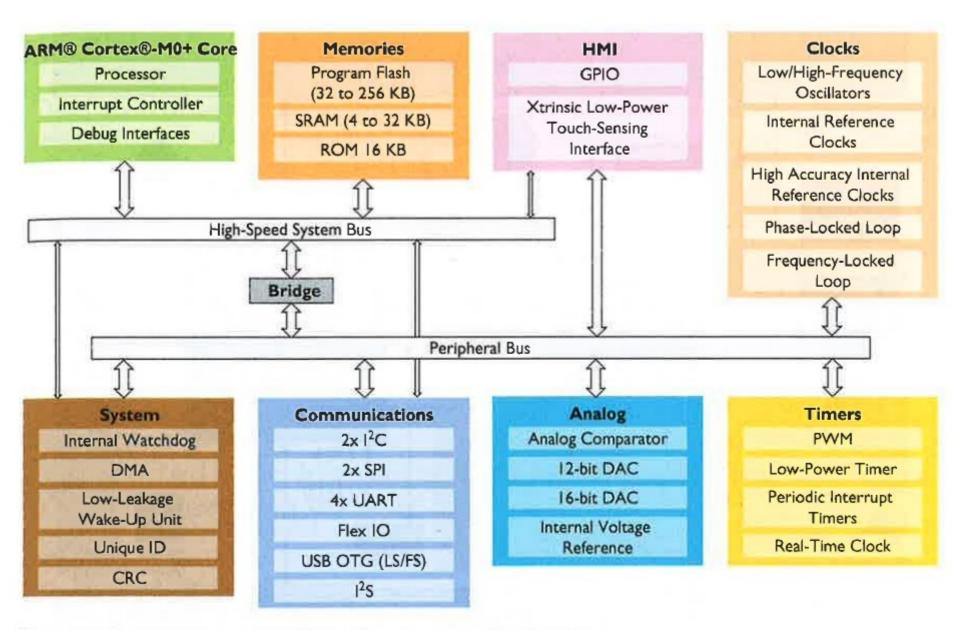

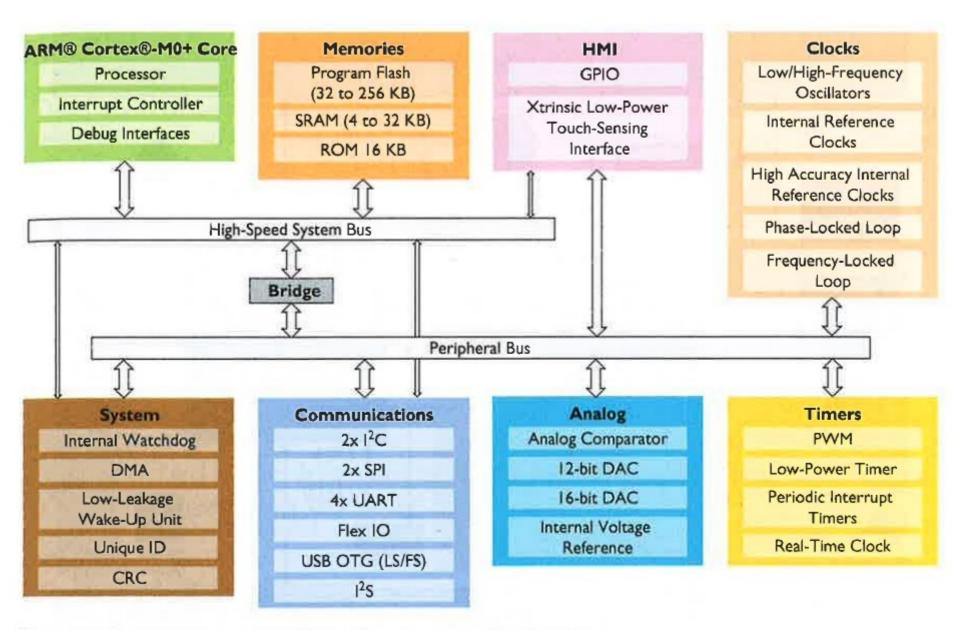

Figure 1.17 NXP Kinetis KL25Z family microcontroller (MCU).

### NXP Processor and FRDM-KL25Z Development Board Documentation

- [1] NXP Kinetis KL25 processor sub-family data sheet (pdf)

[2] NXP Kinetis KL25 processor sub-family reference manual (pdf)

- [3] FRDM-KL25Z development board schematics (pdf)

[4] FRDM-KL25Z development board user manual (pdf)

- [5] Setting up Keil software for a FRDM-KL25Z development board (pdf)

- [6] Header file MKL25Z4.h (.h)

Freescale Semiconductor, Inc.

Data Sheet: Technical Data

Document Number: KL25P80M48SF0

Rev 5 08/2014

## Kinetis KL25 Sub-Family

48 MHz Cortex-M0+ Based Microcontroller with USB

Designed with efficiency in mind. Compatible with all other Kinetis L families as well as Kinetis K2x family. General purpose MCU with USB 2.0, featuring market leading ultra low-power to provide developers an appropriate entry-level 32-bit solution.

This product offers:

- Run power consumption down to 47 μA/MHz in very low power run mode

- Static power consumption down to 2 μA with full state retention and 4 μs wakeup

- Ultra-efficient Cortex-M0+ processor running up to 48 MHz with industry leading throughput

- Memory option is up to 128 KB flash and 16 KB RAM

- Energy-saving architecture is optimized for low power with 90 nm TFS technology, clock and power gating techniques, and zero wait state flash memory controller

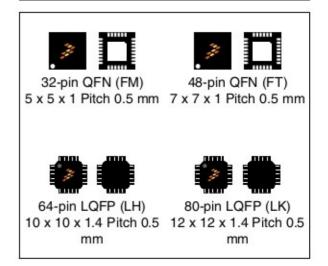

MKL25ZxxVFM4 MKL25ZxxVFT4 MKL25ZxxVLH4 MKL25ZxxVLK4

#### Performance

48 MHz ARM® Cortex®-M0+ core

#### Memories and memory interfaces

- · Up to 128 KB program flash memory

- . Up to 16 KB SRAM

#### Human-machine interface

- Low-power hardware touch sensor interface (TSI)

- Up to 66 general-purpose input/output (GPIO)

#### Communication interfaces

USB full-/low-speed On-the-Go controller with onchip transceiver and 5 V to 3.3 V regulator

# 5.1 KL25 Signal Multiplexing and Pin Assignments

The following table shows the signals available on each pin and the locations of these pins on the devices supported by this document. The Port Control Module is responsible for selecting which ALT functionality is available on each pin.

| 80<br>LQFP | 64<br>LQFP | 48<br>QFN | 32<br>QFN | Pin Name | Default  | ALT0    | ALT1 | ALT2      | ALT3     | ALT4           | ALT5      | ALT6     | ALT7 |

|------------|------------|-----------|-----------|----------|----------|---------|------|-----------|----------|----------------|-----------|----------|------|

| 1          | 1          | -         | 1         | PTE0     | DISABLED |         | PTE0 |           | UART1_TX | RTC_<br>CLKOUT | CMP0_OUT  | I2C1_SDA |      |

| 2          | 2          | -         |           | PTE1     | DISABLED |         | PTE1 | SPI1_MOSI | UART1_RX |                | SPI1_MISO | I2C1_SCL |      |

| 3          | -          | -         | -         | PTE2     | DISABLED |         | PTE2 | SPI1_SCK  |          |                |           |          |      |

| 4          | _          | -         | _         | PTE3     | DISABLED |         | PTE3 | SPI1_MISO |          |                | SPI1_MOSI |          |      |

| 5          | _          | _         | 1-        | PTE4     | DISABLED |         | PTE4 | SPI1_PCS0 |          |                |           |          |      |

| 6          | _          | _         | _         | PTE5     | DISABLED |         | PTE5 |           |          |                |           |          |      |

| 7          | 3          | 1         | _         | VDD      | VDD      | VDD     |      |           |          |                |           |          |      |

| 8          | 4          | 2         | 2         | VSS      | VSS      | VSS     |      |           |          |                |           |          |      |

| 9          | 5          | 3         | 3         | USB0_DP  | USB0_DP  | USB0_DP |      |           |          |                |           |          |      |

| 10         | 6          | 4         | 4         | USB0_DM  | USB0_DM  | USB0_DM |      |           |          |                |           |          |      |

Figure 1.17 NXP Kinetis KL25Z family microcontroller (MCU).

## Some of the circuits that need Input/Output pins

- A/D converter

- D/A converter

- UART (serial I/O)

- I2C

- USB

- SPI

- Input to start/stop a timer

- Pulse width modulation output from timer

- External clock input to timer

- Clock output copy of the system clock

- General Purpose Input Output GPIO

- and others

## Some of the circuits that need Input/Output pins

- A/D converter

- D/A converter

- UART (serial I/O)

- I2C

- USB

- SPI

- Input to start/stop a timer

- Pulse width modulation output from timer

- External clock input to timer

- Clock output copy of the system clock

- General Purpose Input Output GPIO

- and others

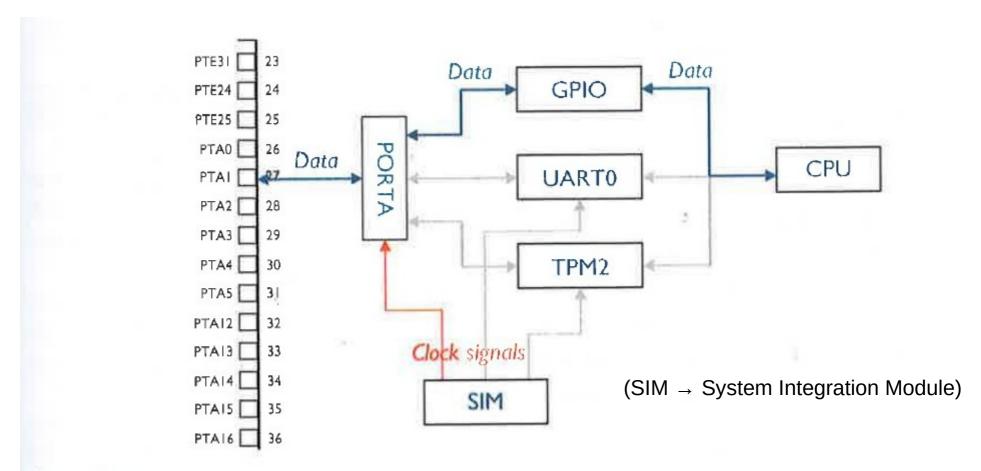

How do all these functions relate to the physical pins on the chip?

First, there are five I/O ports defined in this microcontroller

PortA

**PortB**

PortC

PortD

**PortE**

Each with up to 32 bits

Which means in theory there could be up to  $32 \times 5 = 160$  pins for I/O on the chip

But, not all are used. Limited to available physical pins

Figure 2.6 An overview of hardware between pin PTA1 and the CPU.

## Pinout

| 80<br>LQFP | 64<br>LQFP | 48<br>QFN | 32<br>QFN | Pin Name                       | Default                 | ALT0                    | ALT1                           | ALT2      | ALT3     | ALT4           | ALT5      | ALT6 | ALT7 |

|------------|------------|-----------|-----------|--------------------------------|-------------------------|-------------------------|--------------------------------|-----------|----------|----------------|-----------|------|------|

| 44         | 36         | 28        | 21        | PTB1                           | ADC0_SE9/<br>TSI0_CH6   | ADC0_SE9/<br>TSI0_CH6   | PTB1                           | I2C0_SDA  | TPM1_CH1 |                |           |      |      |

| 45         | 37         | 29        | -         | PTB2                           | ADC0_SE12/<br>TSI0_CH7  | ADC0_SE12/<br>TSI0_CH7  | PTB2                           | I2C0_SCL  | TPM2_CH0 |                |           |      |      |

| 46         | 38         | 30        |           | PTB3                           | ADC0_SE13/<br>TSI0_CH8  | ADC0_SE13/<br>TSI0_CH8  | PTB3                           | I2C0_SDA  | TPM2_CH1 |                |           |      |      |

| 47         |            | 1-        | _         | PTB8                           | DISABLED                |                         | PTB8                           |           | EXTRG_IN |                |           |      |      |

| 48         | -          | -         |           | PTB9                           | DISABLED                |                         | PTB9                           |           |          |                |           |      |      |

| 49         | <b>1</b>   | 1-        | -         | PTB10                          | DISABLED                |                         | PTB10                          | SPI1_PCS0 |          |                |           |      |      |

| 50         | -          | -         | _         | PTB11                          | DISABLED                |                         | PTB11                          | SPI1_SCK  |          |                |           |      |      |

| 51         | 39         | 31        | _         | PTB16                          | TSI0_CH9                | TSI0_CH9                | PTB16                          | SPI1_MOSI | UARTO_RX | TPM_<br>CLKIN0 | SPI1_MISO |      |      |

| 52         | 40         | 32        | _         | PTB17                          | TSI0_CH10               | TSI0_CH10               | PTB17                          | SPI1_MISO | UARTO_TX | TPM_<br>CLKIN1 | SPI1_MOSI |      |      |

| 53         | 41         | -         | _         | PTB18                          | TSI0_CH11               | TSI0_CH11               | PTB18                          |           | TPM2_CH0 |                |           |      |      |

| 54         | 42         | -         | -         | PTB19                          | TSI0_CH12               | TSI0_CH12               | PTB19                          |           | TPM2_CH1 |                |           |      |      |

| 55         | 43         | 33        | =         | PTC0                           | ADC0_SE14/<br>TSI0_CH13 | ADC0_SE14/<br>TSI0_CH13 | PTC0                           |           | EXTRG_IN |                | CMP0_OUT  |      |      |

| 56         | 44         | 34        | 22        | PTC1/<br>LLWU_P6/<br>RTC_CLKIN | ADC0_SE15/<br>TSI0_CH14 | ADC0_SE15/<br>TSI0_CH14 | PTC1/<br>LLWU_P6/<br>RTC_CLKIN | I2C1_SCL  |          | TPM0_CH0       |           |      |      |

Also found in the family data sheet is electrical and timing info. for example, electrical:

## 1.4 Voltage and current operating ratings

Table 4. Voltage and current operating ratings

| Symbol              | Description                                                               | Min.                  | Max.                  | Unit |

|---------------------|---------------------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>DD</sub>     | Digital supply voltage                                                    | -0.3                  | 3.8                   | V    |

| I <sub>DD</sub>     | Digital supply current                                                    |                       | 120                   | mA   |

| V <sub>IO</sub>     | IO pin input voltage                                                      | -0.3                  | V <sub>DD</sub> + 0.3 | V    |

| I <sub>D</sub>      | Instantaneous maximum current single pin limit (applies to all port pins) | -25                   | 25                    | mA   |

| $V_{DDA}$           | Analog supply voltage                                                     | V <sub>DD</sub> - 0.3 | V <sub>DD</sub> + 0.3 | V    |

| V <sub>USB_DP</sub> | USB_DP input voltage                                                      | -0.3                  | 3.63                  | V    |

| V <sub>USB_DM</sub> | USB_DM input voltage                                                      | -0.3                  | 3.63                  | V    |

| V <sub>REGIN</sub>  | USB regulator input                                                       | -0.3                  | 6.0                   | V    |

## 2.2.1 Voltage and current operating requirements

Table 5. Voltage and current operating requirements

| Symbol                             | Description                                                                                                            | Min.                   | Max.                   | Unit | Notes |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|------|-------|

| V <sub>DD</sub>                    | Supply voltage                                                                                                         | 1.71                   | 3.6                    | ٧    |       |

| $V_{DDA}$                          | Analog supply voltage                                                                                                  | 1.71                   | 3.6                    | ٧    | _     |

| $V_{DD} - V_{DDA}$                 | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage                                                              | -0.1                   | 0.1                    | ٧    | _     |

| V <sub>SS</sub> - V <sub>SSA</sub> | V <sub>SS</sub> -to-V <sub>SSA</sub> differential voltage                                                              | -0.1                   | 0.1                    | ٧    | _     |

| V <sub>IH</sub>                    | Input high voltage                                                                                                     |                        | 9                      |      | _     |

|                                    | <ul> <li>2.7 V ≤ V<sub>DD</sub> ≤ 3.6 V</li> </ul>                                                                     | $0.7 \times V_{DD}$    | _                      | V    |       |

|                                    | • 1.7 V ≤ V <sub>DD</sub> ≤ 2.7 V                                                                                      | $0.75 \times V_{DD}$   | -                      | ٧    |       |

| V <sub>IL</sub>                    | Input low voltage                                                                                                      |                        |                        |      | _     |

|                                    | <ul> <li>2.7 V ≤ V<sub>DD</sub> ≤ 3.6 V</li> </ul>                                                                     |                        | 0.35 × V <sub>DD</sub> | V    |       |

|                                    | • 1.7 V ≤ V <sub>DD</sub> ≤ 2.7 V                                                                                      |                        | $0.3 \times V_{DD}$    | V    |       |

| V <sub>HYS</sub>                   | Input hysteresis                                                                                                       | 0.06 × V <sub>DD</sub> |                        | ٧    | _     |

| I <sub>ICIO</sub>                  | IO pin negative DC injection current—single pin  • V <sub>IN</sub> < V <sub>SS</sub> -0.3V                             | -3                     |                        | mA   | 1     |

| I <sub>ICcont</sub>                | Contiguous pin DC injection current —regional limit, includes sum of negative injection currents of 16 contiguous pins |                        |                        |      | _     |

|                                    | Negative current injection                                                                                             | -25                    |                        | mA   |       |

| V <sub>ODPU</sub>                  | Open drain pullup voltage level                                                                                        | V <sub>DD</sub>        | V <sub>DD</sub>        | ٧    | 2     |

| V <sub>RAM</sub>                   | V <sub>DD</sub> voltage required to retain RAM                                                                         | 1.2                    | _                      | ٧    | _     |

### 2.1 AC electrical characteristics

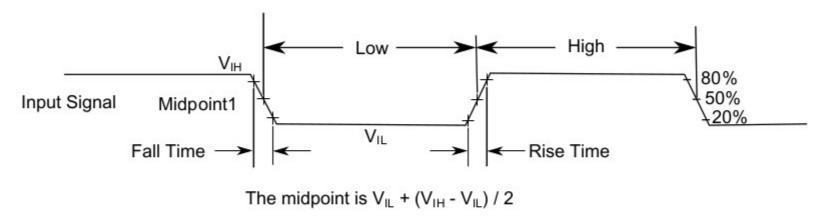

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

Figure 2. Input signal measurement reference

All digital I/O switching characteristics, unless otherwise specified, assume the output pins have the following characteristics.

- C<sub>L</sub>=30 pF loads

- · Slew rate disabled

- Normal drive strength

# 2.3.1 Device clock specifications

Table 13. Device clock specifications

| Symbol               | Description                                            | Min. | Max. | Unit |

|----------------------|--------------------------------------------------------|------|------|------|

|                      | Normal run mode                                        |      |      |      |

| f <sub>SYS</sub>     | System and core clock                                  | _    | 48   | MHz  |

| f <sub>BUS</sub>     | Bus clock                                              | _    | 24   | MHz  |

| f <sub>FLASH</sub>   | Flash clock                                            | _    | 24   | MHz  |

| f <sub>SYS_USB</sub> | System and core clock when Full Speed USB in operation | 20   | _    | MHz  |

| f <sub>LPTMR</sub>   | LPTMR clock                                            | _    | 24   | MHz  |

|                      | VLPR and VLPS modes <sup>1</sup>                       | 4    |      | 9    |

| f <sub>SYS</sub>     | System and core clock                                  | _    | 4    | MHz  |

| f <sub>BUS</sub>     | Bus clock                                              | 1—1  | 1    | MHz  |

| f <sub>FLASH</sub>   | Flash clock                                            | _    | 1    | MHz  |

| f <sub>LPTMR</sub>   | LPTMR clock <sup>2</sup>                               | _    | 24   | MHz  |

### NXP Processor and FRDM-KL25Z Development Board Documentation

- [1] NXP Kinetis KL25 processor sub-family data sheet (pdf)

[2] NXP Kinetis KL25 processor sub-family reference manual (pdf)

[3] FRDM-KL25Z development board schematics (pdf)

[4] FRDM-KL25Z development board user manual (pdf)

- [5] Setting up Keil software for a FRDM-KL25Z development board (pdf)

- [6] Header file MKL25Z4.h (.h)

# KL25 Sub-Family Reference Manual

Supports: MKL25Z32VFM4, MKL25Z64VFM4, MKL25Z128VFM4, MKL25Z32VFT4, MKL25Z64VFT4, MKL25Z128VFT4, MKL25Z32VLH4, MKL25Z64VLH4, MKL25Z128VLH4, MKL25Z32VLK4, MKL25Z64VLK4, and MKL25Z128VLK4

Document Number: KL25P80M48SF0RM

Rev. 3, September 2012

| ➤ Chapter 1: About This Document                                            | 33  |

|-----------------------------------------------------------------------------|-----|

| ▶ Chapter 2: Introduction                                                   | 35  |

| ▶ Chapter 3: Chip Configuration                                             | 45  |

| ▶ Chapter 4: Memory Map                                                     | 105 |

| ▶ Chapter 5: Clock Distribution                                             | 115 |

| ▶ Chapter 6: Reset and Boot                                                 | 127 |

| ▶ Chapter 7: Power Management                                               | 137 |

| ▶ Chapter 8: Security                                                       | 149 |

| ▶ Chapter 9: Debug                                                          | 151 |

| <ul> <li>Chapter 10: Signal Multiplexing and Signal Descriptions</li> </ul> | 159 |

| <ul> <li>Chapter 11: Port control and interrupts (PORT)</li> </ul>          | 175 |

| <ul> <li>Chapter 12: System integration module (SIM)</li> </ul>             | 191 |

| <ul> <li>Chapter 13: System Mode Controller (SMC)</li> </ul>                | 217 |

| <ul> <li>Chapter 14: Power Management Controller (PMC)</li> </ul>           | 237 |

| ▶ Chapter 15: Low-Leakage Wakeup Unit (LLWU)                                | 245 |

| ▶ Chapter 16: Reset Control Module (RCM)                                    | 265 |

| ▶ Chapter 17: Bit Manipulation Engine (BME)                                 | 271 |

| ▶ Chapter 18: Miscellaneous Control Module (MCM)                            | 291 |

| ▶ Chapter 19: Micro Trace Buffer (MTB)                                      | 299 |

| <ul> <li>Chapter 20: Crossbar Switch Lite (AXBS-Lite)</li> </ul>            | 331 |

| <ul><li>Chapter 21: Peripheral Bridge (AIPS-Lite)</li></ul>                 | 335 |

| ▶ Chapter 22: Direct Memory Access Multiplexer (DMAMUX)                     | 337 |

| ▶ Chapter 23: DMA Controller Module                                         | 349 |

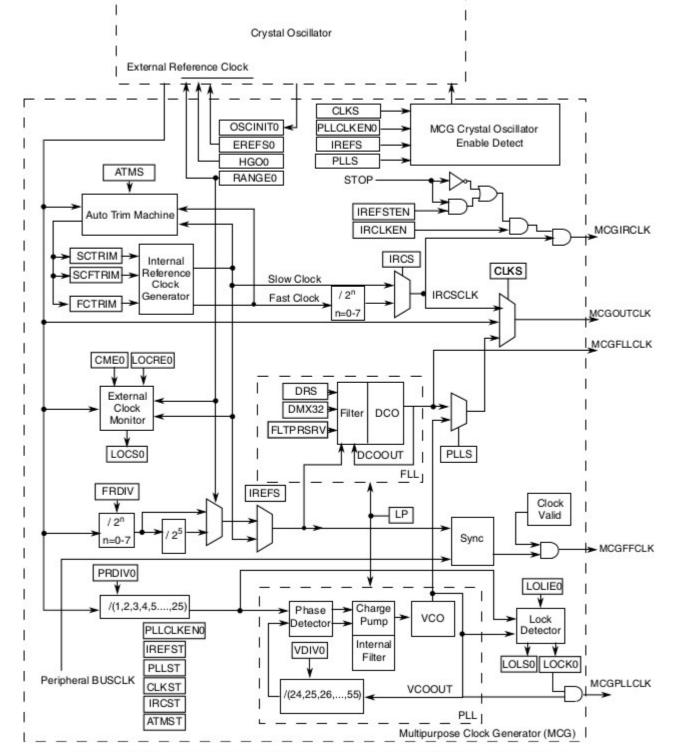

| <ul> <li>Chapter 24: Multipurpose Clock Generator (MCG)</li> </ul>          | 367 |

| ▶ Chapter 25: Oscillator (OSC)                                              | 405 |

| ▶ Chapter 26: Flash Memory Controller (FMC)                                 | 415 |

| ▶ Chapter 27: Flash Memory Module (FTFA)                                    | 419 |

| <ul> <li>Chapter 28: Analog-to-Digital Converter (ADC)</li> </ul>           | 457 |

| ▶ Chapter 29: Comparator (CMP)                                              | 509 |

| ▶ Chapter 30: 12-bit Digital-to-Analog Converter (DAC)                      | 537 |

| ▶ Chapter 31: Timer/PWM Module (TPM)                                        | 547 |

| ▶ Chapter 32: Periodic Interrupt Timer (PIT)                                | 573 |

| ▶ Chapter 33: Low-Power Timer (LPTMR)                                       | 587 |

| ▶ Chapter 34: Real Time Clock (RTC)                                         | 597 |

| ▶ Chapter 35: Universal Serial Bus OTG Controller (USBOTG)                  | 611 |

| ▶ Chapter 36: USB Voltage Regulator                                         | 651 |

| ▶ Chapter 37: Serial Peripheral Interface (SPI)                             | 655 |

| • | Chapter 22: Direct Memory Access Multiplexer (DMAMUX) | 337 |

|---|-------------------------------------------------------|-----|

| ١ | Chapter 23: DMA Controller Module                     | 349 |

| ٠ | Chapter 24: Multipurpose Clock Generator (MCG)        | 367 |

| • | Chapter 25: Oscillator (OSC)                          | 405 |

| • | Chapter 26: Flash Memory Controller (FMC)             | 415 |

Figure 24-1. Multipurpose Clock Generator (MCG) block diagram

## SIM memory map

| Absolute<br>address<br>(hex) | Register name                                      | Width<br>(in bits) | Access | Reset value | Section/<br>page |

|------------------------------|----------------------------------------------------|--------------------|--------|-------------|------------------|

| 4004_7000                    | System Options Register 1 (SIM_SOPT1)              | 32                 | R/W    | See section | 12.2.1/183       |

| 4004_7004                    | SOPTI Configuration Register (SIM_SOPTICFG)        | 32                 | R/W    | 0000_0000h  | 12.2.2/184       |

| 4004_8004                    | System Options Register 2 (SIM_SOPT2)              | 32                 | R/W    | 0000_0000h  | 12.2.3/185       |

| 4004_800C                    | System Options Register 4 (SIM_SOPT4)              | 32                 | R/W    | 0000_0000h  | 12.2.4/187       |

| 4004_8010                    | System Options Register 5 (SIM_SOPT5)              | 32                 | R/W    | 0000_0000h  | 12.2.5/189       |

| 4004_8018                    | System Options Register 7 (SIM_SOPT7)              | 32                 | R/W    | 0000_0000h  | 12.2.6/190       |

| 4004_8024                    | System Device Identification Register (SIM_SDID)   | 32                 | R      | Undefined   | 12.2.7/192       |

| 4004_8034                    | System Clock Gating Control Register 4 (SIM_SCGC4) | 32                 | R/W    | F000_0030h  | 12.2.8/193       |

| 4004_8038                    | System Clock Gating Control Register 5 (SIM_SCGC5) | 32                 | R/W    | 0000_0180h  | 12.2.9/195       |

| 4004_803C                    | System Clock Gating Control Register 6 (SIM_SCGC6) | 32                 | R/W    | 0000_0001h  | 12.2.10/197      |

| 4004_8040                    | System Clock Gating Control Register 7 (SIM_SCGC7) | 32                 | R/W    | 0000_0100h  | 12.2.11/199      |

Figure 2.4 A portion of registers for the System Integration Module (SIM) peripheral [1, p. 182].

### NXP Processor and FRDM-KL25Z Development Board Documentation

- [1] NXP Kinetis KL25 processor sub-family data sheet (pdf)

[2] NXP Kinetis KL25 processor sub-family reference manual (pdf)

[3] FRDM-KL25Z development board schematics (pdf)

[4] FRDM-KL25Z development board user manual (pdf)

- [5] Setting up Keil software for a FRDM-KL25Z development board (pdf)

- [6] Header file MKL25Z4.h (.h)

#### I/O Header 5V 3.3V Vin CR2032 3.3V LDO 1/0 PWM x3 Mini-B USB USB D+/D-Touch Pad - Slider Mini-B USB UART D+/D-USB Kinetis L-Series SPI,GPIO → SWD Kinetis K-Series TSI KL25Z128VLK4 K20DX128VFM5 80 LQFP 10-pin RESET Debug 8 MHz Serial SPI 8 MHz Flash I2C, GPIO 1/0 10-pin Debug Inertial **OpenSDA** Sensor

I/O Header