#### Chapter 2 - part 4

Instructions: Language of the Computer Addressing modes Synchronization Program creation

# **Register Usage**

- \$a0 \$a3: arguments (reg's 4 7)

- \$v0, \$v1: result values (reg's 2 and 3)

- \$t0 \$t9: temporaries

- Can be overwritten by callee

- \$s0 \$s7: saved

- Must be saved/restored by callee

- \$gp: global pointer for static data (reg 28)

- \$sp: stack pointer (reg 29)

- \$fp: frame pointer (reg 30)

- \$ra: return address (reg 31)

# **Byte/Halfword Operations**

- Could use bitwise operations

- MIPS byte/halfword load/store

- String processing is a common case

- lb rt, offset(rs) lh rt, offset(rs)

- Sign extend to 32 bits in rt

lbu rt, offset(rs) lhu rt, offset(rs)

- Zero extend to 32 bits in rt

- sb rt, offset(rs) sh rt, offset(rs)

- Store just rightmost byte/halfword

#### **32-bit Constants**

- Most constants are small

- 16-bit immediate is sufficient

- For the occasional 32-bit constant

- lui rt, constant

- Copies 16-bit constant to left 16 bits of rt

- Clears right 16 bits of rt to 0

| lhi | \$s0, | 61    |      | 0000 0000 0111 1101 | 0000 0000 0000 0000 |

|-----|-------|-------|------|---------------------|---------------------|

| ori | \$s0, | \$s0, | 2304 | 0000 0000 0111 1101 | 0000 1001 0000 0000 |

### **Branch Addressing**

- Branch instructions specify

- Opcode, two registers, target address

- Most branch targets are near branch

- Forward or backward

| ор     | rs     | rt     | constant or address |

|--------|--------|--------|---------------------|

| 6 bits | 5 bits | 5 bits | 16 bits             |

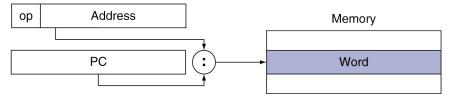

- PC-relative addressing

- Target address = PC + offset × 4

- PC already incremented by 4 by this time

# **Jump Addressing**

- Jump (j and jal) targets could be anywhere in text segment

- Encode full address in instruction

| ор     | address |  |  |

|--------|---------|--|--|

| 6 bits | 26 bits |  |  |

- (Pseudo)Direct jump addressing

- Target address = PC<sub>31...28</sub>: (address × 4)

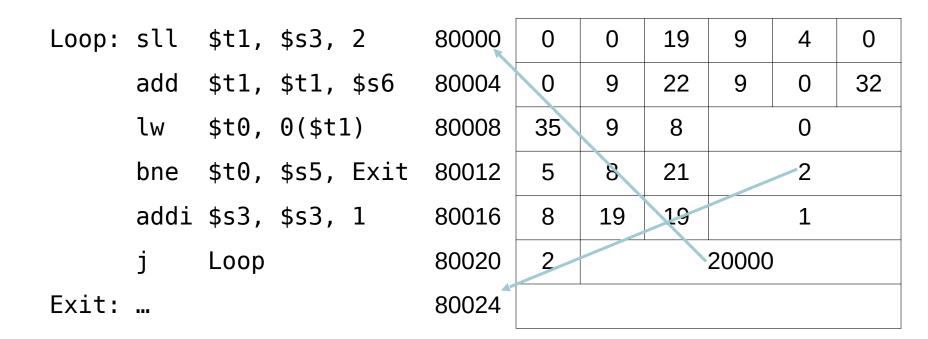

### **Target Addressing Example**

- Loop code from earlier example

- Assume Loop at location 80000

### **Branching Far Away**

If branch target is too far to encode with 16-bit offset, assembler rewrites the code

#### Example

```

beq $s0,$s1, L1

↓

bne $s0,$s1, L2

j L1

L2: ...

```

### **Addressing Mode Summary**

1. Immediate addressing

|  | ор | rs | rt | Immediate |

|--|----|----|----|-----------|

|--|----|----|----|-----------|

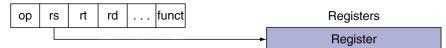

#### 2. Register addressing

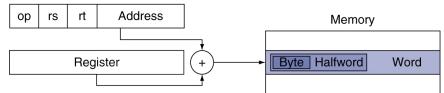

#### 3. Base addressing

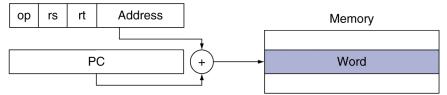

#### 4. PC-relative addressing

#### 5. Pseudodirect addressing

Chapter 2 — Instructions: Language of the Computer — 9

# **Synchronization**

- Two processors sharing an area of memory

- P1 writes, then P2 reads

- Data race if P1 and P2 don't synchronize

- Result depends of order of accesses

- Hardware support required

- Atomic read/write memory operation

- Atomic → No other access to the location allowed between the read and write

- Could be a single instruction

- E.g., atomic swap of register  $\leftrightarrow$  memory

- Or an atomic pair of instructions

# **Synchronization in MIPS**

- Load linked: ll rt, offset(rs)

- Store conditional: sc rt, offset(rs)

- Succeeds if location not changed since the ll

- Returns 1 in rt

- Fails if location is changed

- Returns 0 in rt

- Example: atomic swap (to test/set lock variable)

- try: add \$t0,\$zero,\$s4 ;copy exchange value

- ll \$t1,0(\$s1) ;load linked

- sc \$t0,0(\$s1) ;store conditional

- beq \$t0,\$zero,try ;branch store fails

- add \$s4,\$zero,\$t1 ;put load value in \$s4

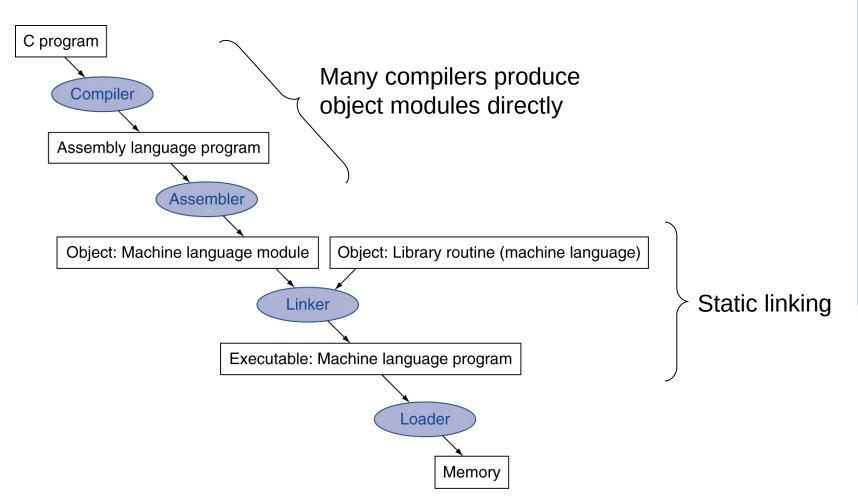

#### **Translation and Startup**

#### **Assembler Pseudoinstructions**

- Most assembler instructions represent machine instructions one-to-one

- Pseudoinstructions: figments of the assembler's imagination

move \$t0, \$t1  $\rightarrow$  add \$t0, \$zero, \$t1 blt \$t0, \$t1, L  $\rightarrow$  slt \$at, \$t0, \$t1 bne \$at, \$zero, L

\$at (register 1): assembler temporary