# **Today's topics**

Components of a computer

- CPU

- (Memory)

- (Input)

- (Output)

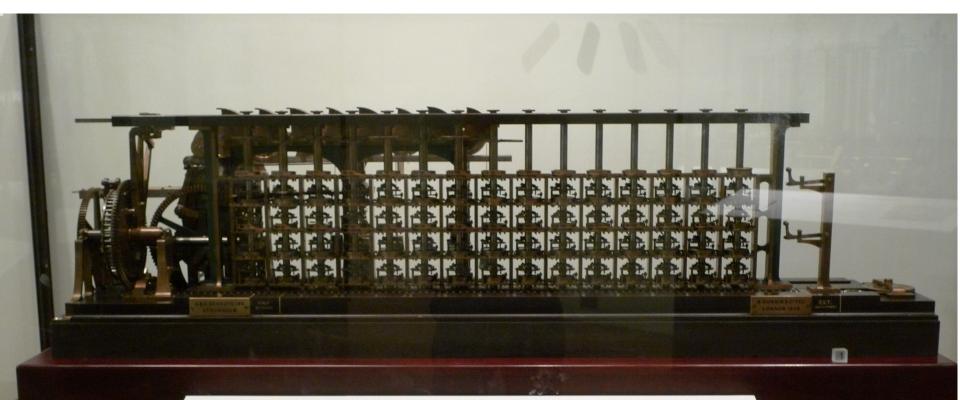

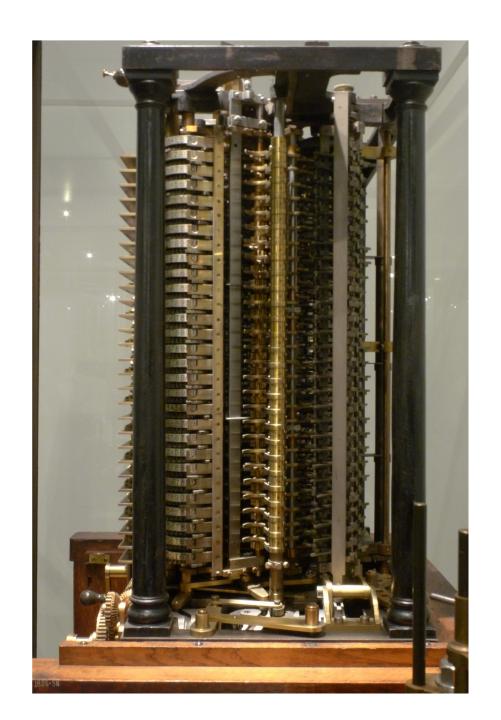

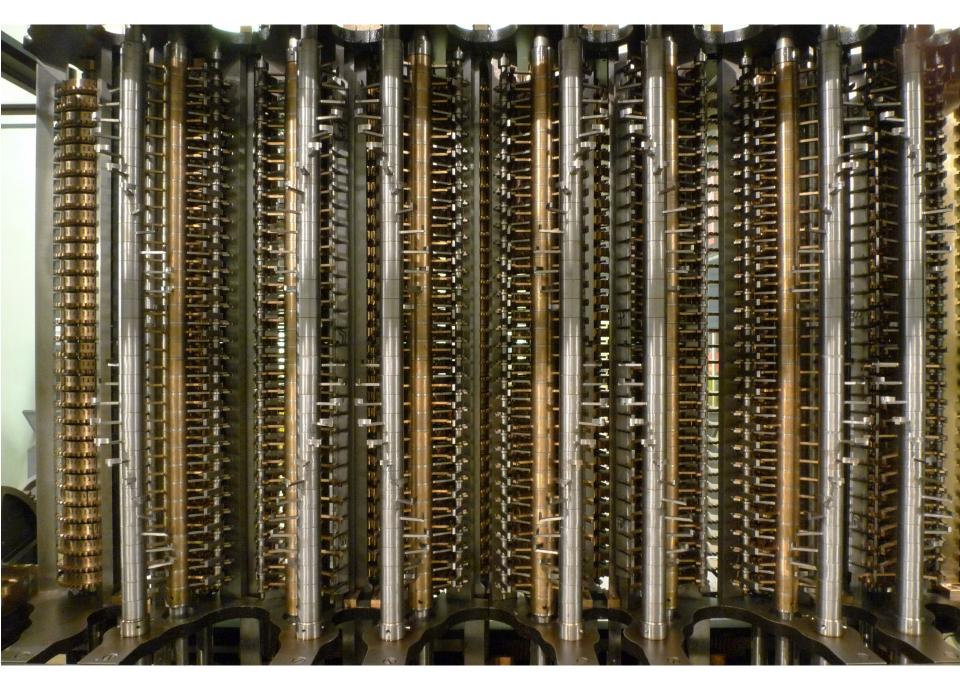

#### The world's first working Difference Engines

Charles Babbage

Calculating Machine

London

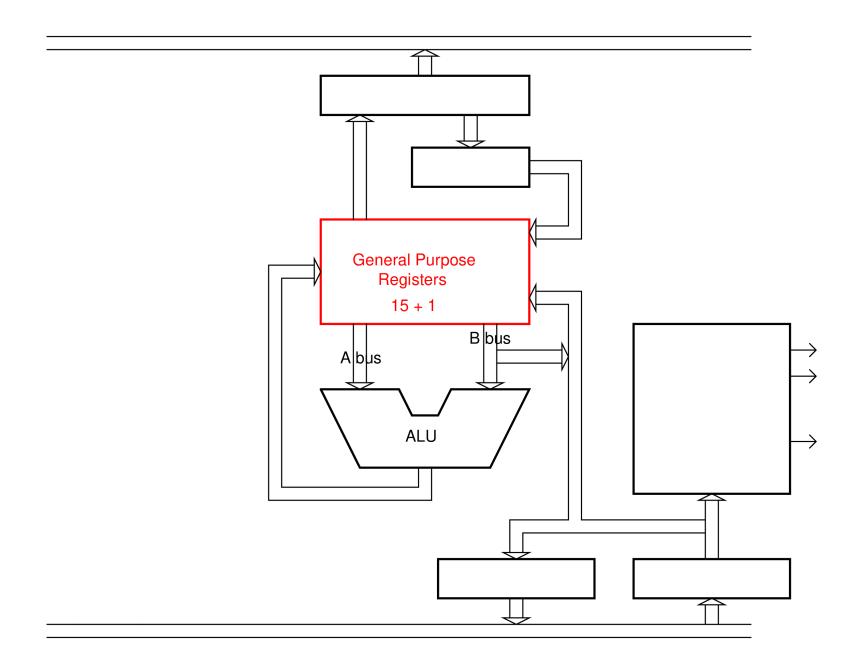

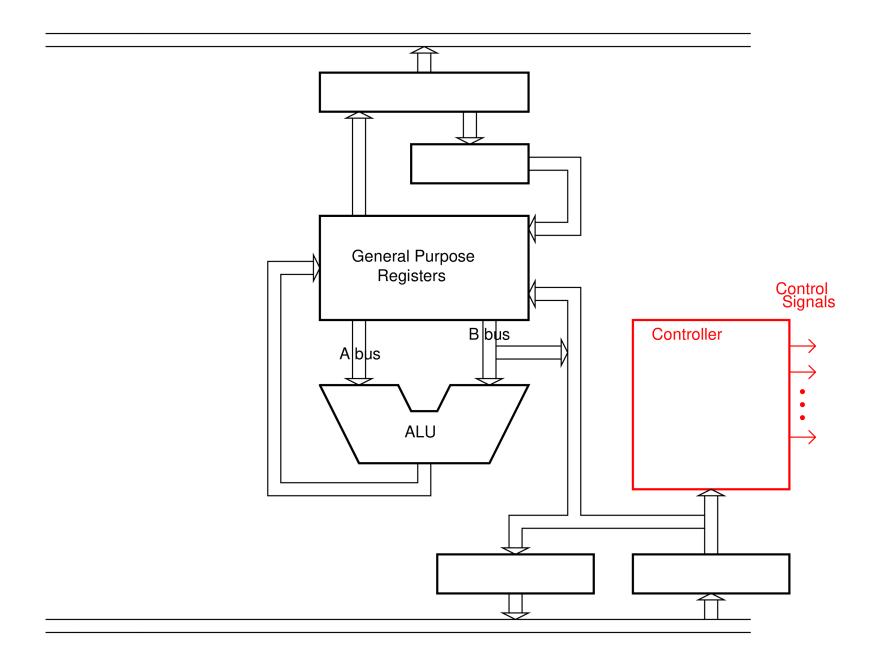

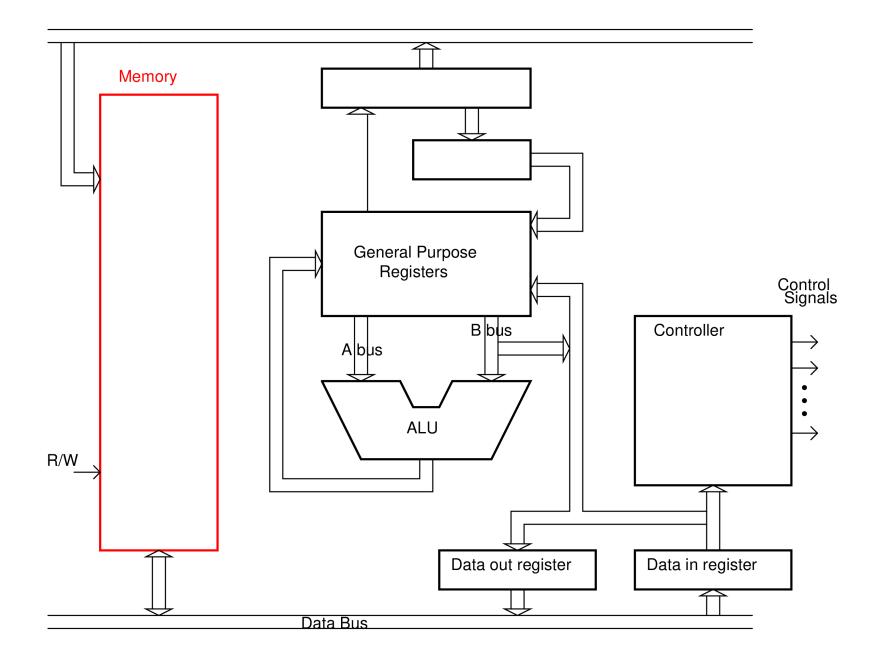

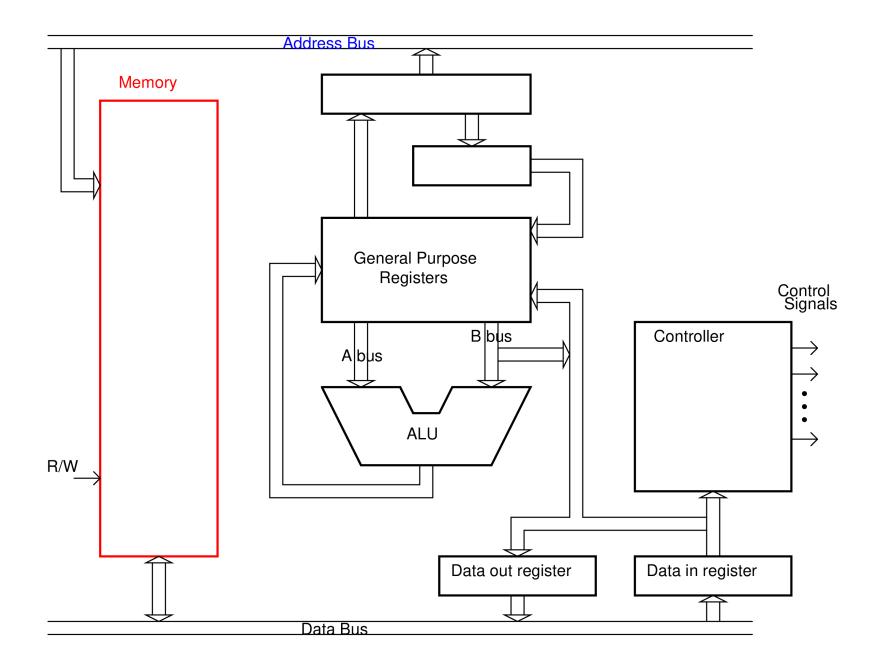

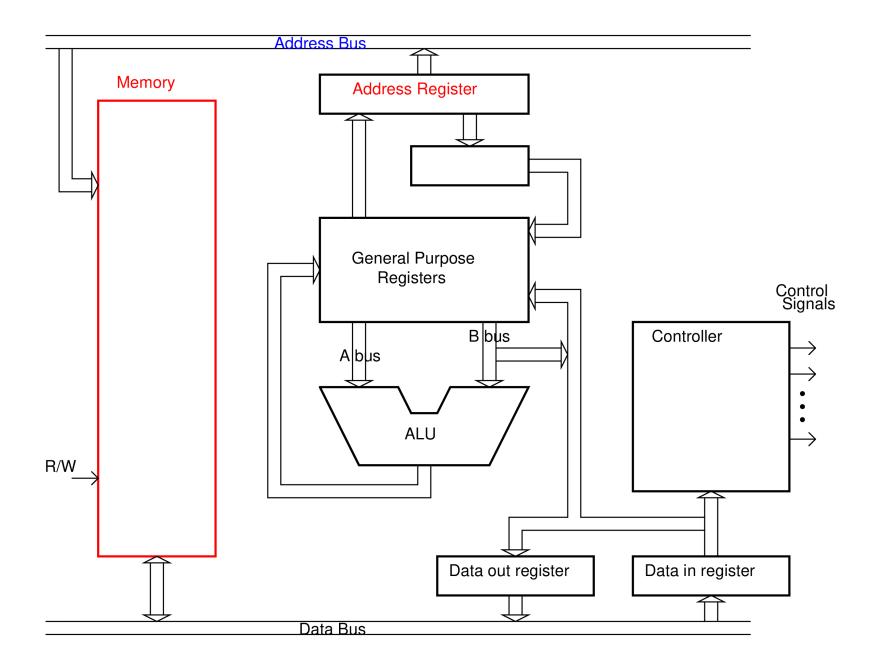

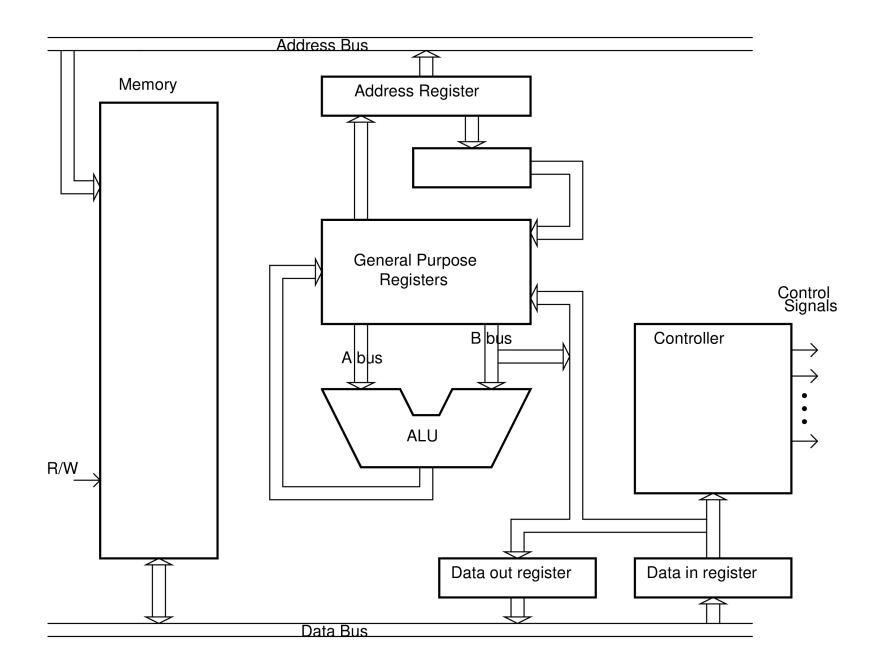

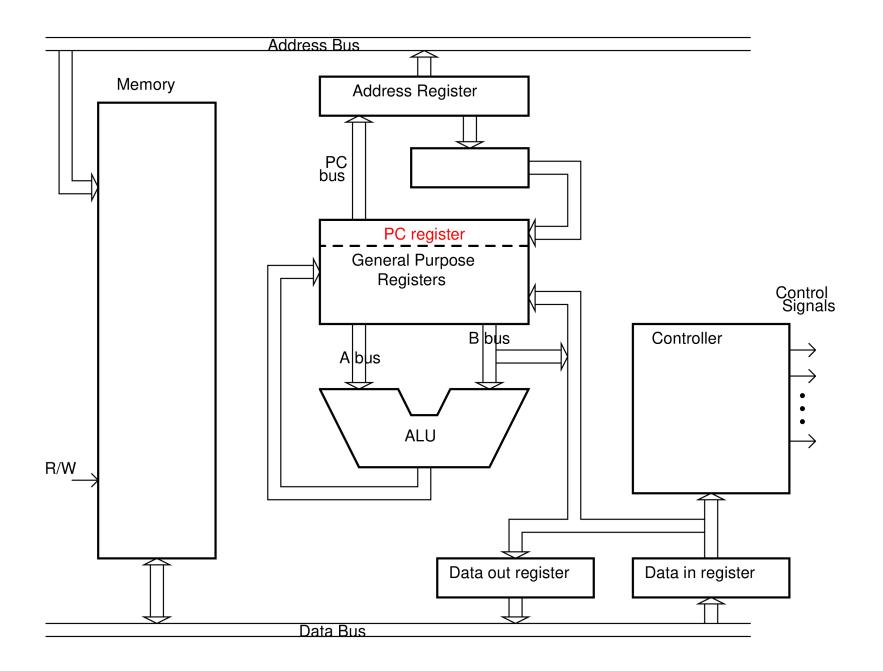

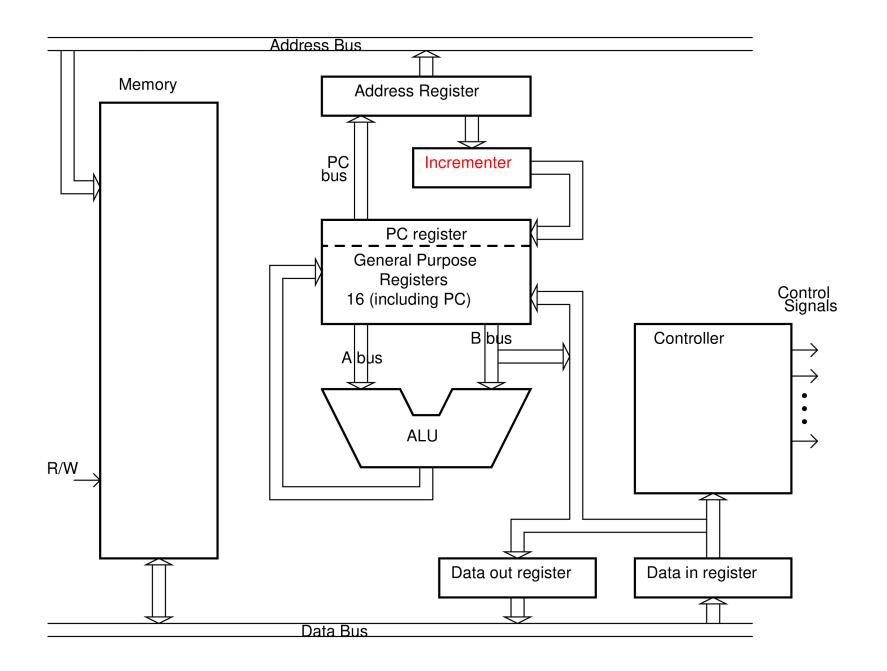

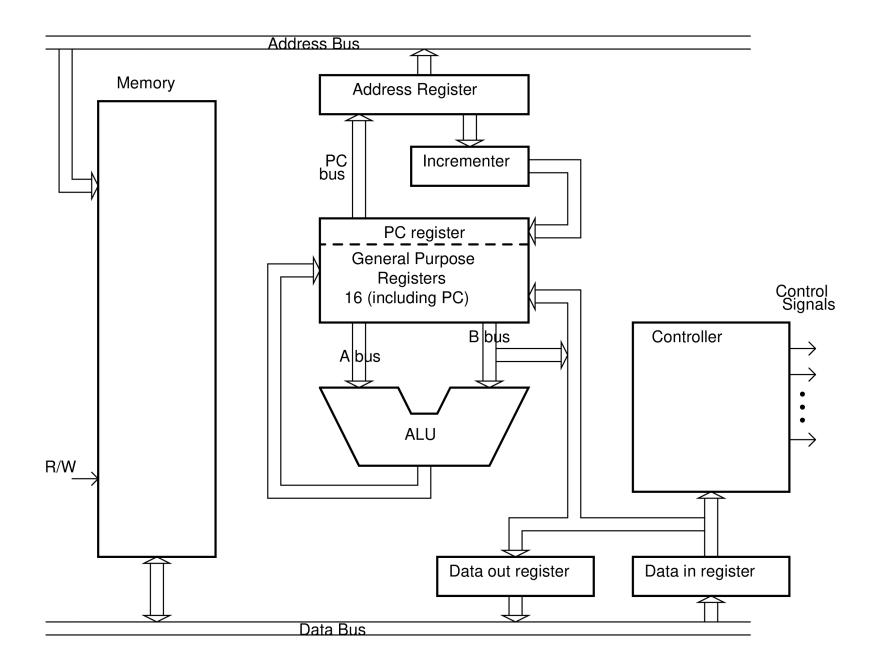

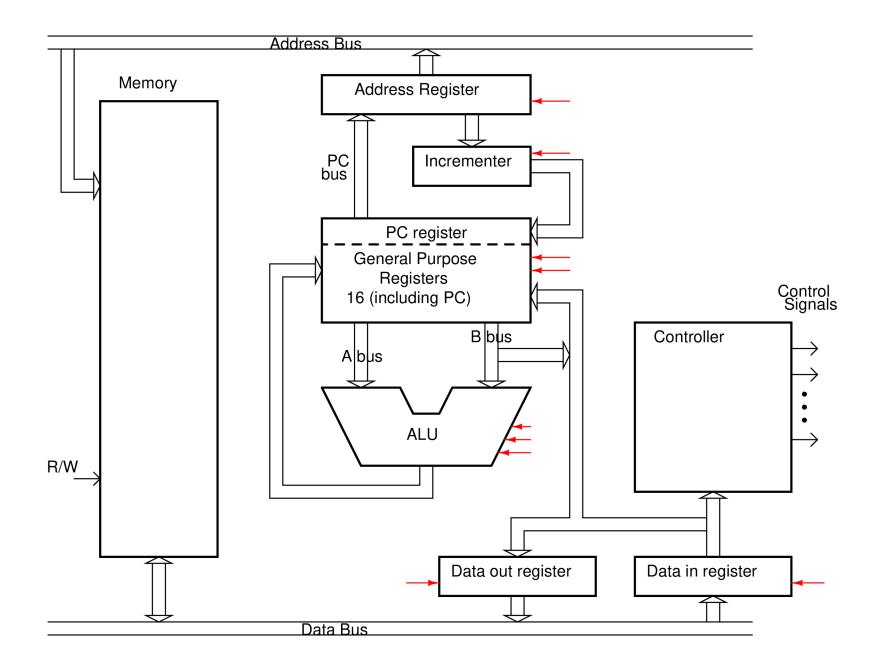

# **Inside the Processor (CPU)**

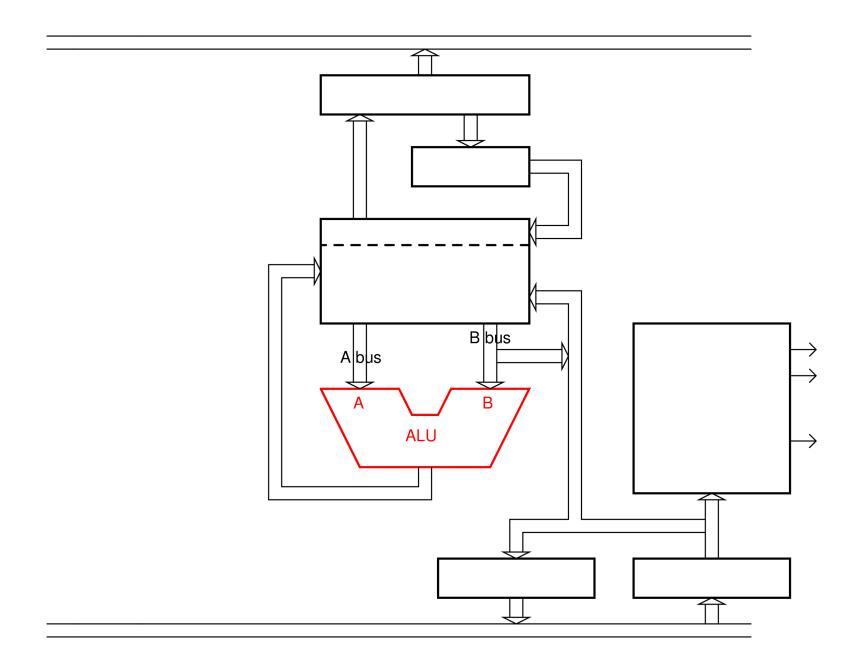

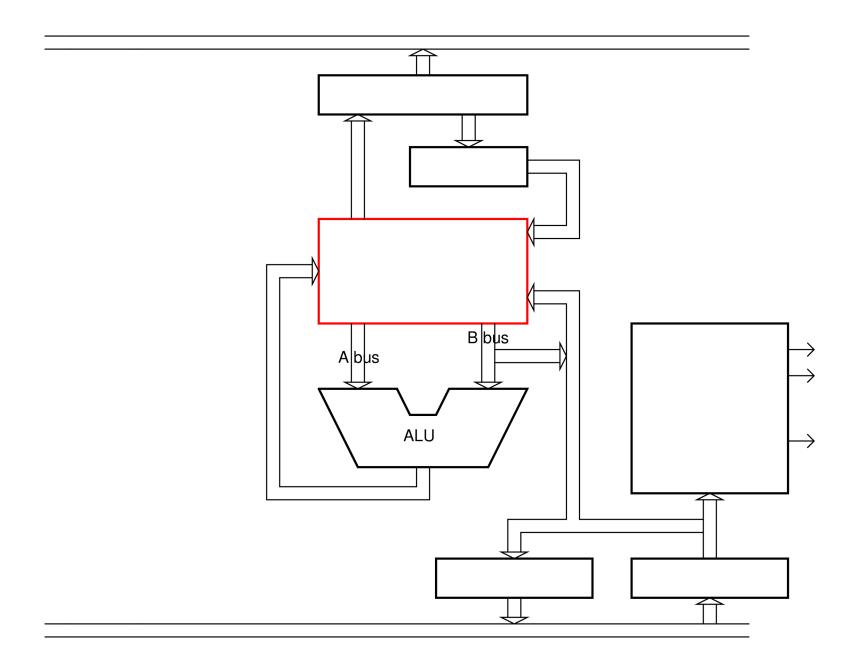

Datapath: performs operations on data Control: sequences datapath, memory, ... Cache memory

Small fast SRAM memory for immediate access to data

### The Aamodt Simple Machine

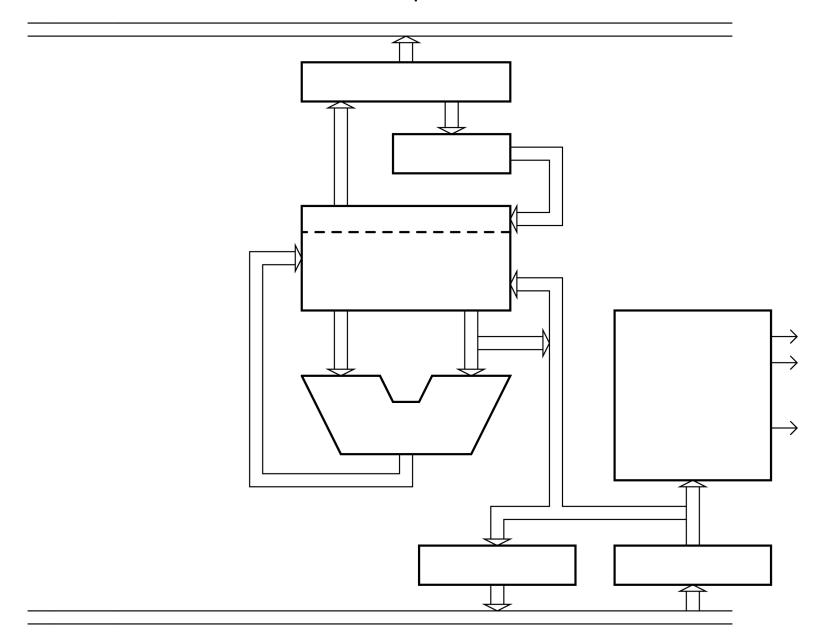

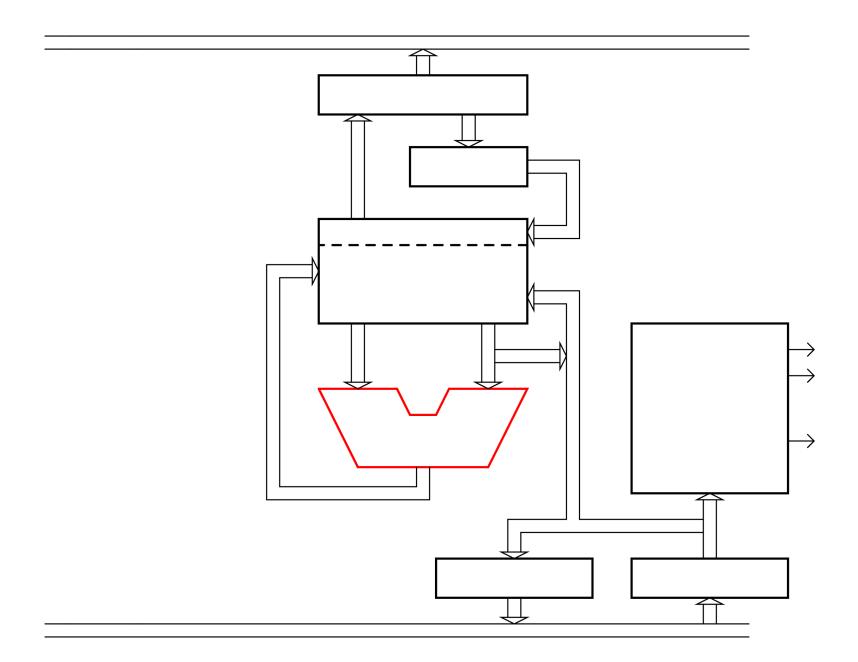

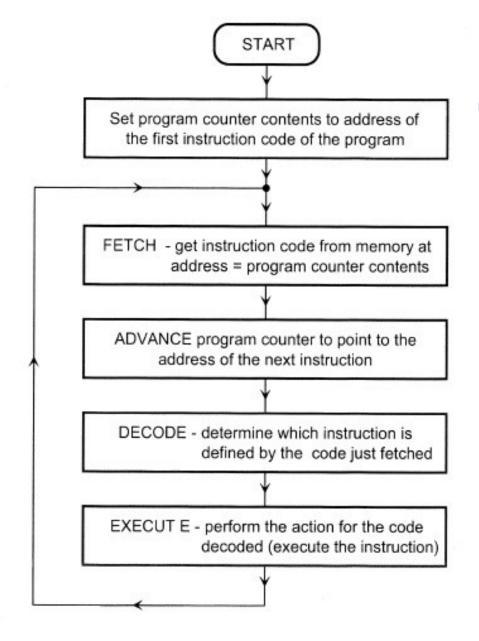

Figure 3.3 Detailed von Neumann cycle sequence

$Syntax: \\ ADD\{<cond>\}\{S\} < Rd>, < Rn>, < shifter\_operand> \\$

Encoding:

| 31 | 30   | 29 | 28 | 27            | 26 | 25 | 24 | 23 | 22 | 21   | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13              | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|------|----|----|---------------|----|----|----|----|----|------|----|----|----|----|----|----|----|-----------------|----|----|----|---|---|---|---|---|---|---|---|---|---|

|    | cond |    |    | 0 0 1 0 1 0 0 |    |    |    | 0  | S  | S Rn |    |    |    | Rd |    |    |    | shifter operand |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                                          | 31 30 29 28 | 27      | 26 | 25 | 24                         | 23                        | 22                   | 21  | 20  | 19 18 17 16 | 15 14 13 12 | 11        | 10     | 9  | 8      | 7 | 6     | 5  | 4   | 3   | 3   | 2    | 1 0 |

|------------------------------------------|-------------|---------|----|----|----------------------------|---------------------------|----------------------|-----|-----|-------------|-------------|-----------|--------|----|--------|---|-------|----|-----|-----|-----|------|-----|

| Multiply (accumulate)                    | cond        | 0       | 0  | 0  | 0                          | 0                         | 0                    | Α   | S   | Rd          | Rn          | Rs        |        |    |        | 1 | 0     | 0  | 0 1 |     | Rm  |      |     |

| Multiply (accumulate) long               | cond        | 0       | 0  | 0  | 0                          | 1                         | U                    | Α   | S   | Rd_MSW      | Rd_LSW      | Rn        |        |    | 1      | 0 | 0     | 1  | 1 R |     | Rm  | 1    |     |

| Branch and exchange                      | cond        | 0       | 0  | 0  | 1                          | 0                         | 0                    | 1   | 0   | 1 1 1 1     | 1 1 1 1     | 1         | 1      | 1  | 1      | 0 | 0     | 0  | 1   |     |     | Rn   |     |

| Single data swap                         | cond        | 0       | 0  | 0  | 1                          | 0                         | В                    | 0   | 0   | Rn          | Rd          | 0         | 0      | 0  | 0      | 1 | 0     | 0  | 1   |     |     | Rm   | 1   |

| Halfword data transfer, register offset  | cond        | 0       | 0  | 0  | Р                          | U                         | 0                    | w   | L   | Rn          | Rd          | 0         | 0      | 0  | 0      | 1 | 0     | 1  | 1   | Π   |     | Rm   | 1   |

| Halfword data transfer, immediate offset | cond        | 0       | 0  | 0  | Р                          | U                         | U 1 W L Rn Rd offset |     |     |             | 1           | 0         | 1      | 1  |        | C | offse | et |     |     |     |      |     |

| Signed data transfer (byte/halfword)     | cond        | 0       | 0  | 0  | Р                          | U                         | В                    | W   | L   | Rn          | Rd          | addr_mode |        |    | 1      | 1 | Н     | 1  | а   | dd  | r_n | node |     |

| Data processing and PSR transfer         | cond        | 0       | 0  | 1  | (                          | opcode S Rn Rd ope        |                      |     |     |             |             | per       | erand2 |    |        |   |       |    |     |     |     |      |     |

| Load/store register/unsigned byte        | cond        | 0       | 1  | 1  | Р                          | P U B W L Rn Rd addr_mode |                      |     |     |             |             |           | ğ      |    |        |   |       |    |     |     |     |      |     |

| Undefined                                | cond        | 0       | 1  | 1  | 1                          |                           |                      |     |     |             |             |           |        |    |        |   |       |    |     |     |     |      |     |

| Block data transfer                      | cond        | 1       | 0  | 0  | P U 0 W L Rn register list |                           |                      |     |     |             |             |           |        |    |        |   |       |    |     |     |     |      |     |

| Branch                                   | cond        | 1       | 0  | 1  | L offset                   |                           |                      |     |     |             |             |           |        |    |        |   |       |    |     |     |     |      |     |

| Coprocessor data transfer                | cond        | 1       | 1  | 0  | Р                          | U N W L Rn                |                      |     |     | CRd         | CP#         |           |        |    | offset |   |       |    |     |     |     |      |     |

| Coprocessor data operation               | cond        | 1 1 1 0 |    | CF | CP opcod                   |                           |                      | CRn | CRd |             | CP#         |           |        |    | СР     |   | 0     |    | (   | CRr | n   |      |     |

| Coprocessor register transfer            | cond        | 1       | 1  | 1  | 0                          | CF                        | o ol                 | рс  | L   | CRn         | Rd          |           | CF     | P# |        |   | СР    |    | 1   |     | (   | CRr  | n   |

| Software interrupt                       | cond        | 1       | 1  | 1  | ignored by processor       |                           |                      |     |     |             |             |           |        |    |        |   |       |    |     |     |     |      |     |

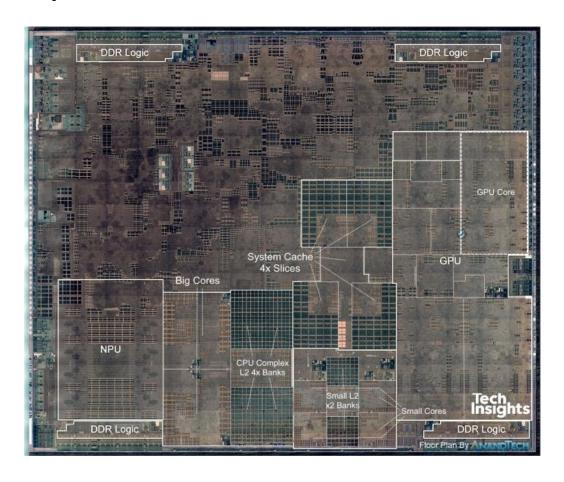

## **Inside the Processor**

### A12 processor